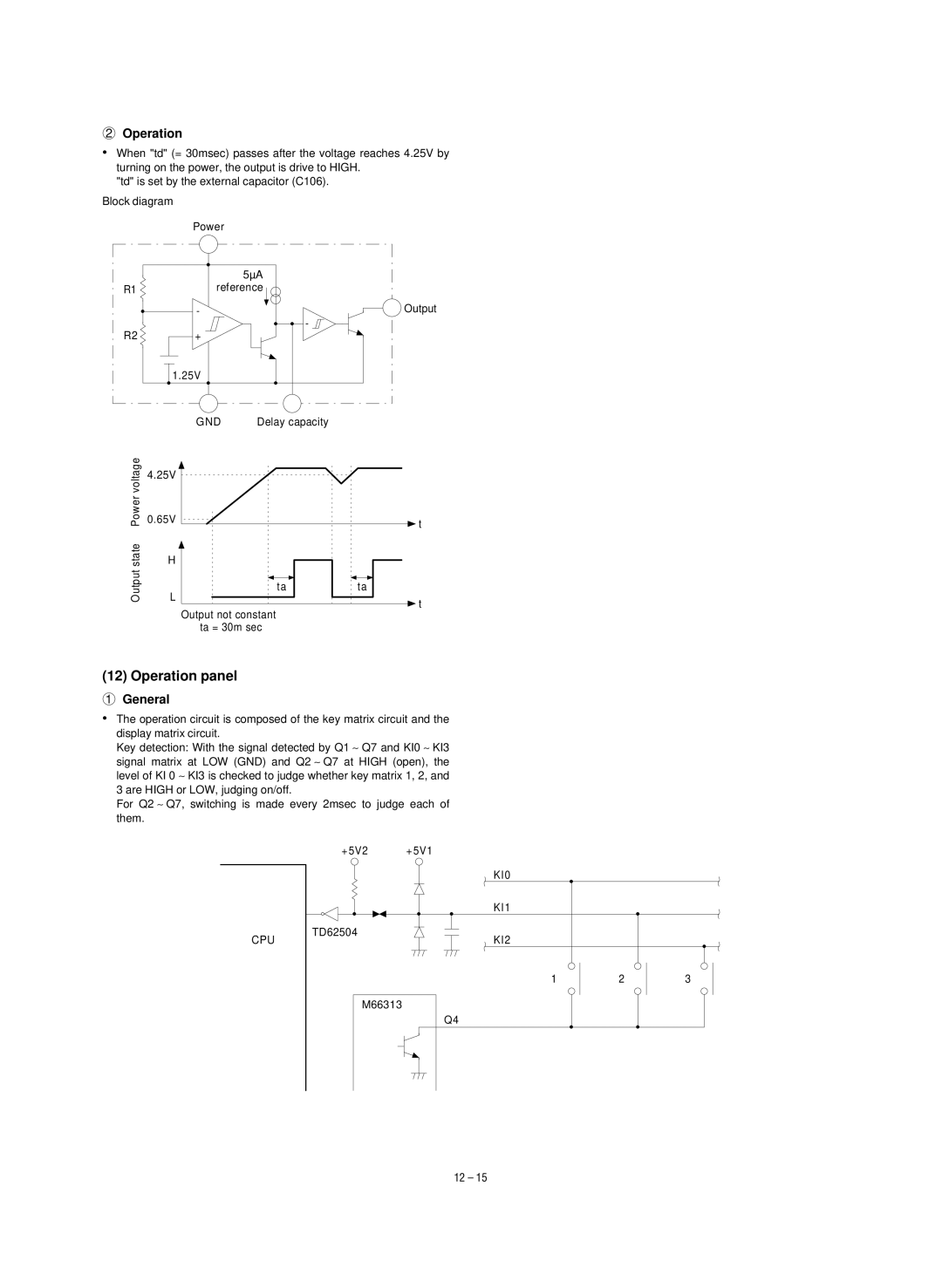

2Operation

•When "td" (= 30msec) passes after the voltage reaches 4.25V by turning on the power, the output is drive to HIGH.

"td" is set by the external capacitor (C106).

Block diagram

| Power |

|

|

| 5µA |

R1 | reference | |

| - | Output |

R2 |

| - |

+ |

| |

| 1.25V |

|

| GND | Delay capacity |

Powervoltage | 4.25V |

|

0.65V | t | |

|

| |

state | H |

|

Output | ta | ta |

L | t | |

|

|

Output not constant ta = 30m sec

(12) Operation panel

1General

•The operation circuit is composed of the key matrix circuit and the

display matrix circuit.

Key detection: With the signal detected by Q1 ∼ Q7 and KI0 ∼ KI3 signal matrix at LOW (GND) and Q2 ∼ Q7 at HIGH (open), the level of KI 0 ∼ KI3 is checked to judge whether key matrix 1, 2, and

3 are HIGH or LOW, judging on/off.

For Q2 ∼ Q7, switching is made every 2msec to judge each of them.

+5V2 | +5V1 |

|

|

| KI0 |

|

|

| KI1 |

|

|

TD62504 | KI2 |

|

|

CPU |

|

| |

| 1 | 2 | 3 |

M66313 |

|

|

|

| Q4 |

|

|

12 – 15