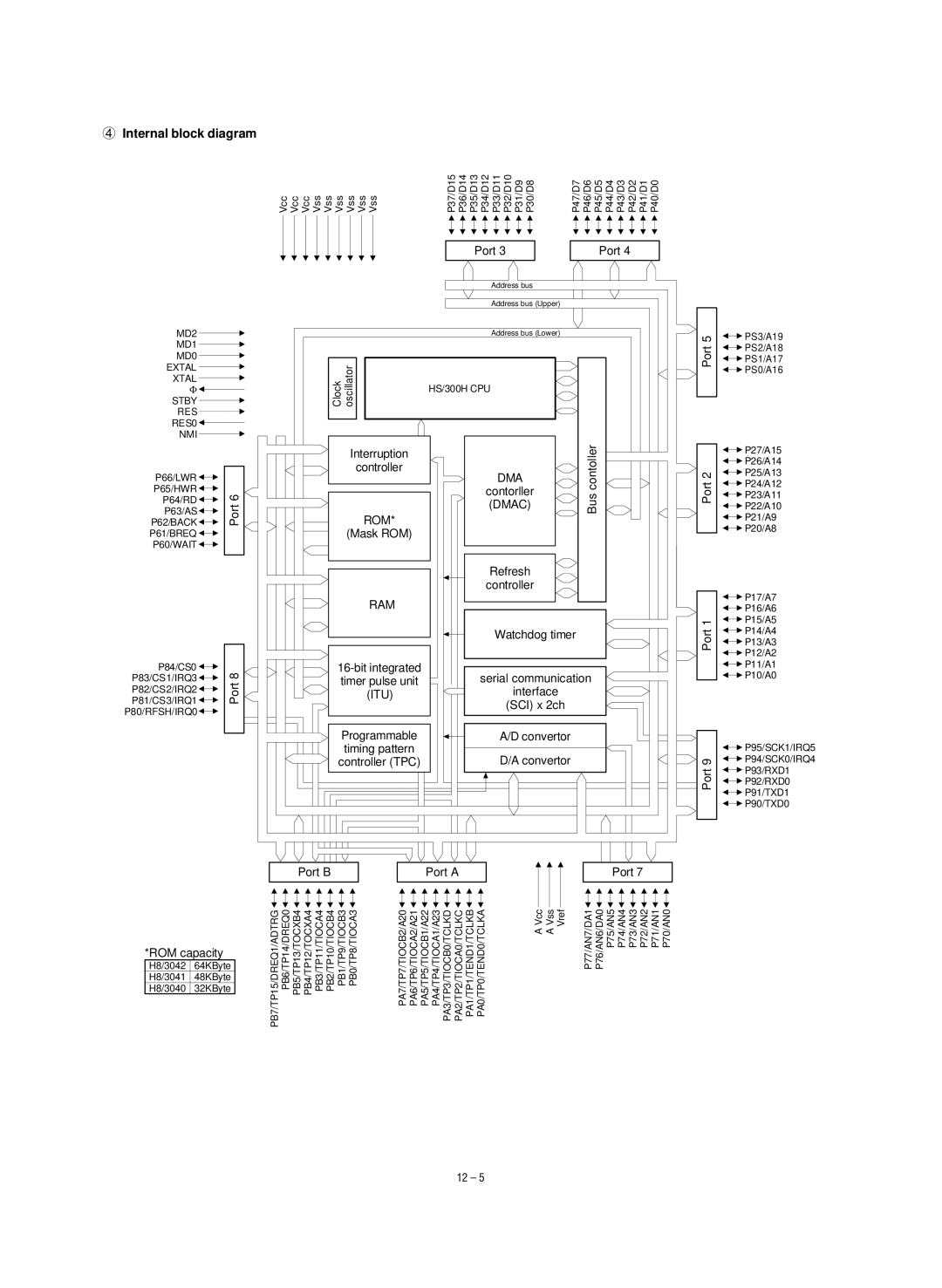

4Internal block diagram

Vcc Vcc Vcc Vss Vss Vss Vss Vss Vss | P37/D15 P36/D14 P35/D13 P34/D12 P33/D11 P32/D10 P31/D9 P30/D8 | P47/D7 P46/D6 P45/D5 P44/D4 P43/D3 P42/D2 P41/D1 P40/D0 |

MD2

MD1

MD0

EXTAL

XTAL Φ ![]()

STBY

RES

RES0 ![]()

NMI

P66/LWR |

| |

P65/HWR | 6 | |

P64/RD | ||

Port | ||

P62/BACK | ||

P63/AS |

| |

P61/BREQ |

| |

P60/WAIT |

|

P84/CS0 | 8 | |

P83/CS1/IRQ3 | ||

Port | ||

P82/CS2/IRQ2 | ||

P81/CS3/IRQ1 | ||

P80/RFSH/IRQ0 |

|

| Port 3 |

| Port 4 |

| Address bus |

|

|

| Address bus (Upper) |

|

|

| Address bus (Lower) |

|

|

Clock oscillator | HS/300H CPU |

|

|

|

|

| |

Interruption |

| contoller |

|

|

|

| |

controller | DMA |

|

|

|

|

| |

| contorller | Bus |

|

| (DMAC) |

| |

|

|

| |

ROM* |

|

|

|

(Mask ROM) |

|

|

|

| Refresh |

|

|

| controller |

|

|

RAM |

|

|

|

| Watchdog timer |

|

|

serial communication |

| ||

timer pulse unit |

| ||

(ITU) | interface |

|

|

| (SCI) x 2ch |

|

|

Programmable | A/D convertor |

|

|

timing pattern | D/A convertor |

|

|

controller (TPC) |

|

| |

5 | PS3/A19 | |

Port | PS2/A18 | |

PS1/A17 | ||

| ||

| PS0/A16 |

| P27/A15 | |

| P26/A14 | |

2 | P25/A13 | |

Port | P24/A12 | |

P23/A11 | ||

| ||

| P22/A10 | |

| P21/A9 | |

| P20/A8 |

| P17/A7 | |

| P16/A6 | |

1 | P15/A5 | |

Port | P14/A4 | |

P13/A3 | ||

| ||

| P12/A2 | |

| P11/A1 | |

| P10/A0 | |

| P95/SCK1/IRQ5 | |

9 | P94/SCK0/IRQ4 | |

Port | P93/RXD1 | |

P92/RXD0 | ||

| ||

| P91/TXD1 | |

| P90/TXD0 |

*ROM capacity

H8/3042 64KByte

H8/3041 48KByte

H8/3040 32KByte

Port B

PB7/TP15/DREQ1/ADTRG | PB6/TP14/DREQ0 | PB5/TP13/TOCXB4 | PB4/TP12/TOCXA4 | PB3/TP11/TIOCA4 | PB2/TP10/TIOCB4 | PB1/TP9/TIOCB3 | PB0/TP8/TIOCA3 |

Port A

PA7/TP7/TIOCB2/A20 | PA6/TP6/TIOCA2/A21 | PA5/TP5/TIOCB1/A22 | PA4/TP4/TIOCA1/A23 | PA3/TP3/TIOCB0/TCLKD | PA2/TP2/TIOCA0/TCLKC | PA1/TP1/TEND1/TCLKB | PA0/TP0/TEND0/TCLKA |

| Port 7 |

A Vcc A Vss Vref | P77/AN7/DA1 P76/AN6/DA0 P75/AN5 P74/AN4 P73/AN3 P72/AN2 P71/AN1 P70/AN0 |

12 – 5