Chapter 1

Table |

| ||||

|

|

|

|

|

|

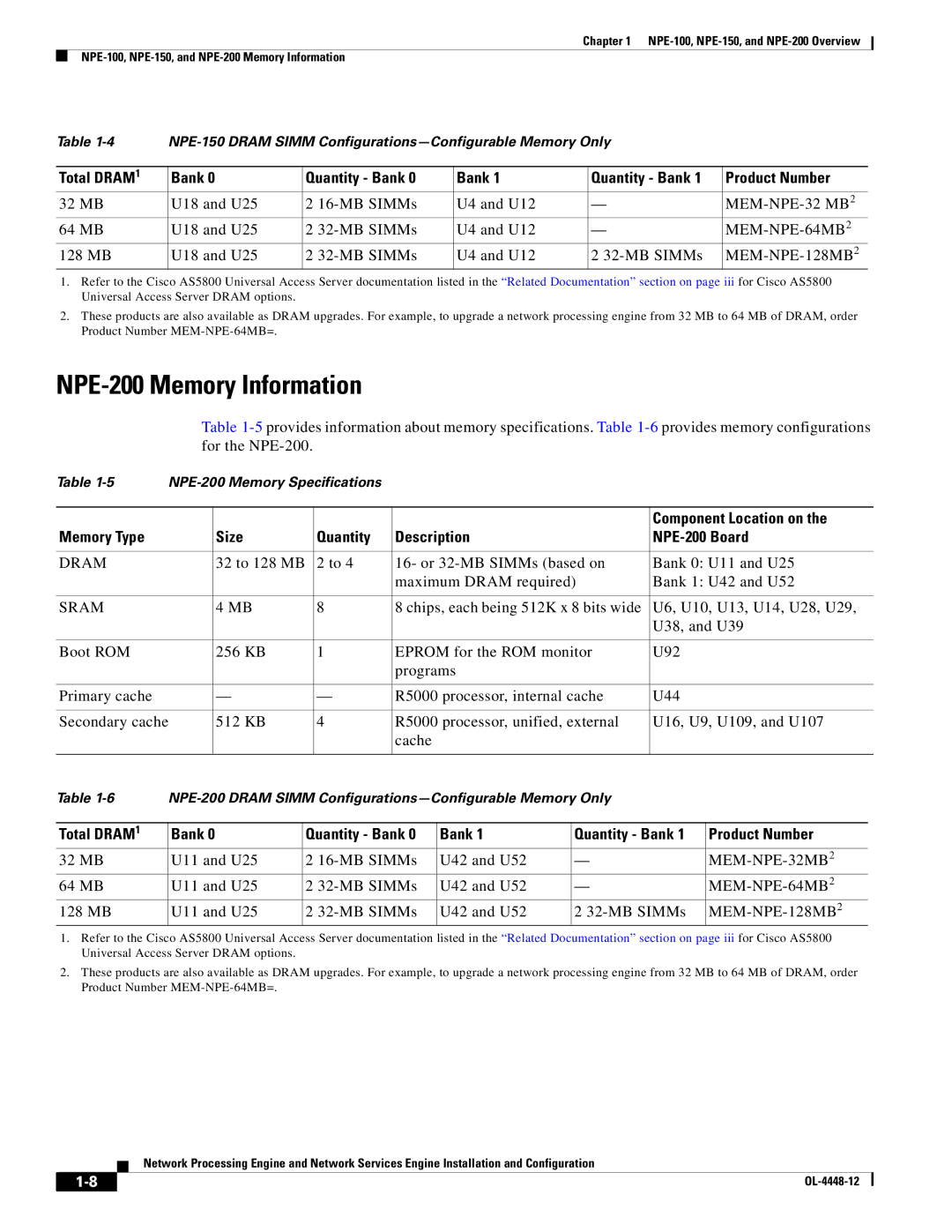

Total DRAM1 | Bank 0 | Quantity - Bank 0 | Bank 1 | Quantity - Bank 1 | Product Number |

32 MB | U18 and U25 | 2 | U4 and U12 | — |

|

64 MB | U18 and U25 | 2 | U4 and U12 | — | |

128 MB | U18 and U25 | 2 | U4 and U12 | 2 |

|

1.Refer to the Cisco AS5800 Universal Access Server documentation listed in the “Related Documentation” section on page iii for Cisco AS5800 Universal Access Server DRAM options.

2.These products are also available as DRAM upgrades. For example, to upgrade a network processing engine from 32 MB to 64 MB of DRAM, order Product Number

NPE-200 Memory Information

Table

Table |

|

| |||

|

|

|

|

|

|

|

|

|

|

| Component Location on the |

Memory Type |

| Size | Quantity | Description |

|

|

|

|

|

|

|

DRAM |

| 32 to 128 MB | 2 to 4 | 16- or | Bank 0: U11 and U25 |

|

|

|

| maximum DRAM required) | Bank 1: U42 and U52 |

|

|

|

|

|

|

SRAM |

| 4 MB | 8 | 8 chips, each being 512K x 8 bits wide | U6, U10, U13, U14, U28, U29, |

|

|

|

|

| U38, and U39 |

|

|

|

|

|

|

Boot ROM |

| 256 KB | 1 | EPROM for the ROM monitor | U92 |

|

|

|

| programs |

|

|

|

|

|

|

|

Primary cache |

| — | — | R5000 processor, internal cache | U44 |

|

|

|

|

| |

Secondary cache | 512 KB | 4 | R5000 processor, unified, external | U16, U9, U109, and U107 | |

|

|

|

| cache |

|

|

|

|

|

|

|

Table |

| ||||

|

|

|

|

|

|

Total DRAM1 | Bank 0 | Quantity - Bank 0 | Bank 1 | Quantity - Bank 1 | Product Number |

32 MB | U11 and U25 | 2 | U42 and U52 | — | |

64 MB | U11 and U25 | 2 | U42 and U52 | — | |

128 MB | U11 and U25 | 2 | U42 and U52 | 2 |

|

1.Refer to the Cisco AS5800 Universal Access Server documentation listed in the “Related Documentation” section on page iii for Cisco AS5800 Universal Access Server DRAM options.

2.These products are also available as DRAM upgrades. For example, to upgrade a network processing engine from 32 MB to 64 MB of DRAM, order Product Number

Network Processing Engine and Network Services Engine Installation and Configuration

|

| |

|