Chapter 3

cisco 7206VXR (NPE400) processor (revision 0xFF) with 122880K/8192K bytes of memory.

Processor board ID 8771013

R7000 CPU at 350Mhz, Implementation 39, Rev 2.1, 256KB L2, 4096KB L3 Cache 6 slot VXR midplane, Version 2.1

(display text omitted)

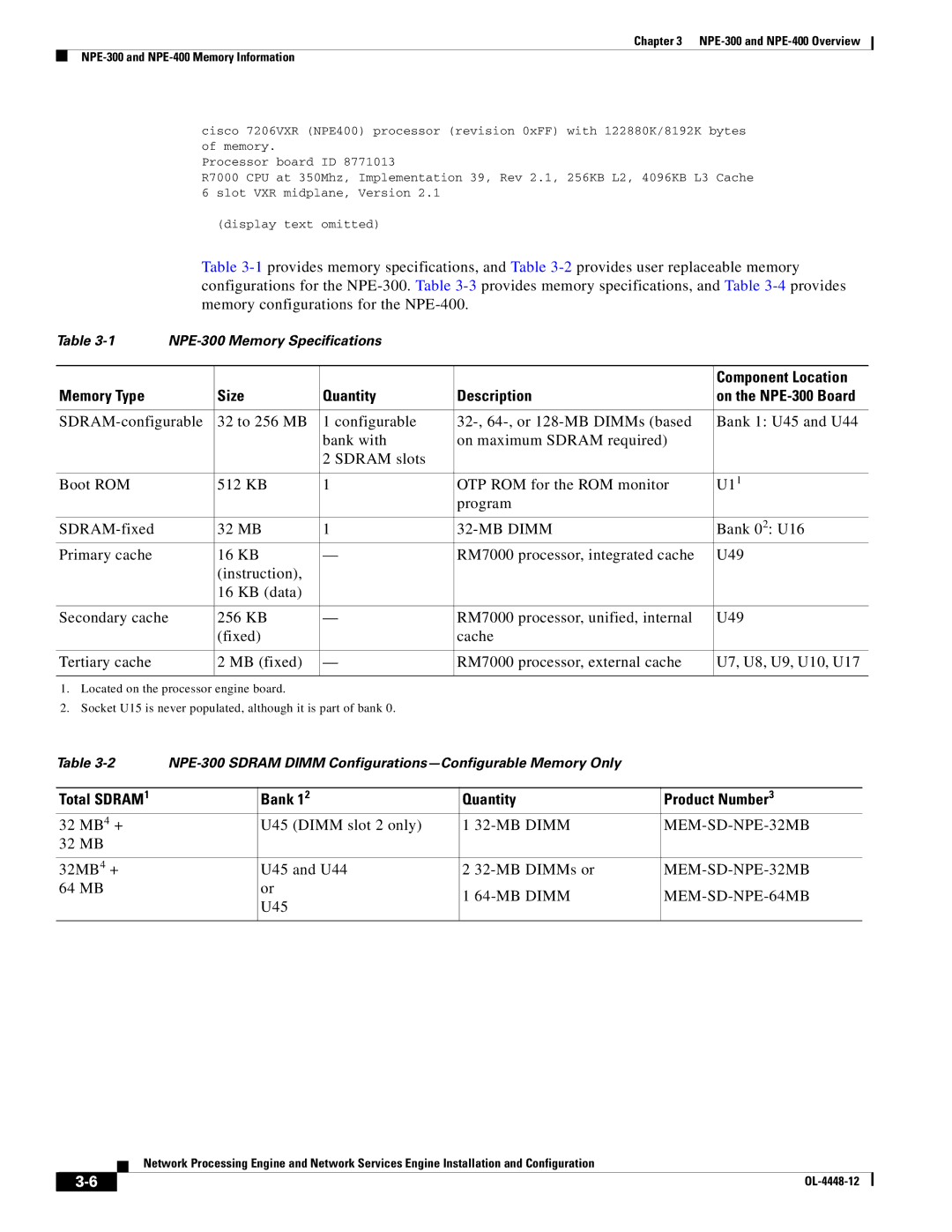

Table

Table |

|

| |||

|

|

|

|

|

|

|

|

|

|

| Component Location |

Memory Type |

| Size | Quantity | Description | on the |

|

|

|

|

| |

32 to 256 MB | 1 configurable | Bank 1: U45 and U44 | |||

|

|

| bank with | on maximum SDRAM required) |

|

|

|

| 2 SDRAM slots |

|

|

|

|

|

|

|

|

Boot ROM |

| 512 KB | 1 | OTP ROM for the ROM monitor | U11 |

|

|

|

| program |

|

|

|

|

|

|

|

| 32 MB | 1 |

| Bank 02: U16 | |

Primary cache |

| 16 KB | — | RM7000 processor, integrated cache | U49 |

|

| (instruction), |

|

|

|

|

| 16 KB (data) |

|

|

|

|

|

|

|

| |

Secondary cache | 256 KB | — | RM7000 processor, unified, internal | U49 | |

|

| (fixed) |

| cache |

|

|

|

|

|

|

|

Tertiary cache |

| 2 MB (fixed) | — | RM7000 processor, external cache | U7, U8, U9, U10, U17 |

|

|

|

|

|

|

1.Located on the processor engine board.

2.Socket U15 is never populated, although it is part of bank 0.

Table |

| |||

|

|

|

|

|

Total SDRAM1 |

| Bank 12 | Quantity | Product Number3 |

32 MB4 + |

| U45 (DIMM slot 2 only) | 1 |

|

32 MB |

|

|

|

|

|

|

|

|

|

32MB4 + |

| U45 and U44 | 2 | |

64 MB |

| or | 1 |

|

|

| U45 | ||

|

|

|

| |

|

|

|

|

|

Network Processing Engine and Network Services Engine Installation and Configuration

|

| |

|