www.ti.com |

| Registers | |

| Table 52. Transmit CPPI Completion Pointer (TCPPICOMPPTR) Field Descriptions | ||

Bit | Field | Value | Description |

DESC_ADDR | Descriptor Address | ||

|

|

| This field contains the |

|

|

| DMA has last processed |

1 | Reserved | 0 | Reserved |

0 | WRBK_MODE |

| Writeback/Compare Mode. This bit controls the action that is to be taken when this location |

|

|

| is written. |

0Compare Mode. Indicates that the value that is presented on bits 31:2 of the write data should be compared against the value that is currently contained in bits 31:2 of this location. If the two match, the interrupt bit corresponding to this Tx Queue should be deasserted.

1Writeback Mode. Indicates that the value that is presented on bits 31:2 of the write data should be written to this location and the interrupt for this Tx Queue should be asserted. This bit is read as zero.

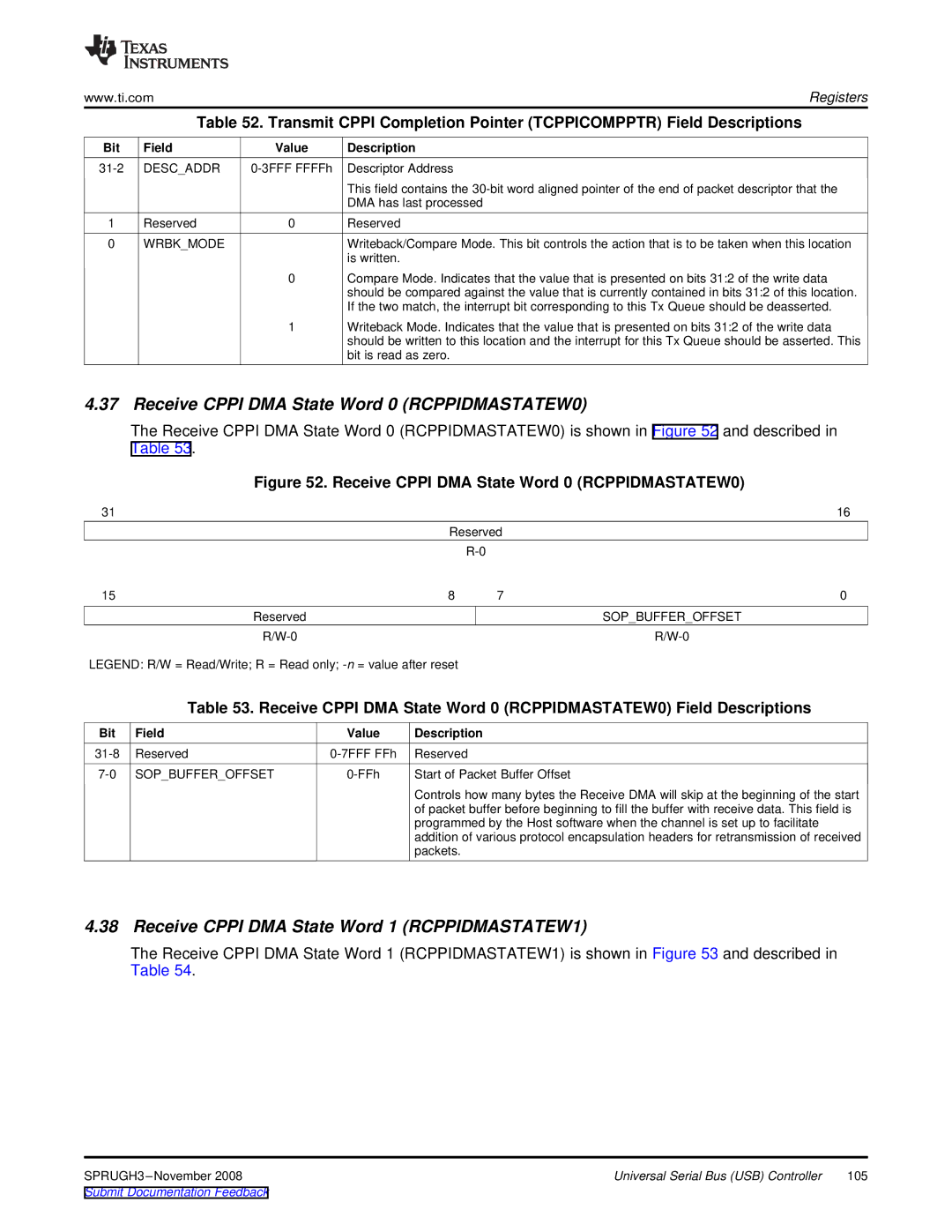

4.37Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0)

The Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0) is shown in Figure 52 and described in Table 53.

Figure 52. Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0)

31 |

|

|

|

| 16 |

|

|

| Reserved |

| |

|

|

|

|

| |

15 |

|

| 8 | 7 | 0 |

| Reserved |

|

| SOP_BUFFER_OFFSET |

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

| |||

| Table 53. Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0) Field Descriptions |

| |||

Bit | Field | Value | Description |

|

|

Reserved | Reserved |

|

| ||

SOP_BUFFER_OFFSET |

| Start of Packet Buffer Offset |

| ||

|

|

| Controls how many bytes the Receive DMA will skip at the beginning of the start | ||

|

|

| of packet buffer before beginning to fill the buffer with receive data. This field is | ||

|

|

| programmed by the Host software when the channel is set up to facilitate |

| |

|

|

| addition of various protocol encapsulation headers for retransmission of received | ||

|

|

| packets. |

|

|

4.38 Receive CPPI DMA State Word 1 (RCPPIDMASTATEW1)

The Receive CPPI DMA State Word 1 (RCPPIDMASTATEW1) is shown in Figure 53 and described in Table 54.

Universal Serial Bus (USB) Controller | 105 |