Registers | www.ti.com |

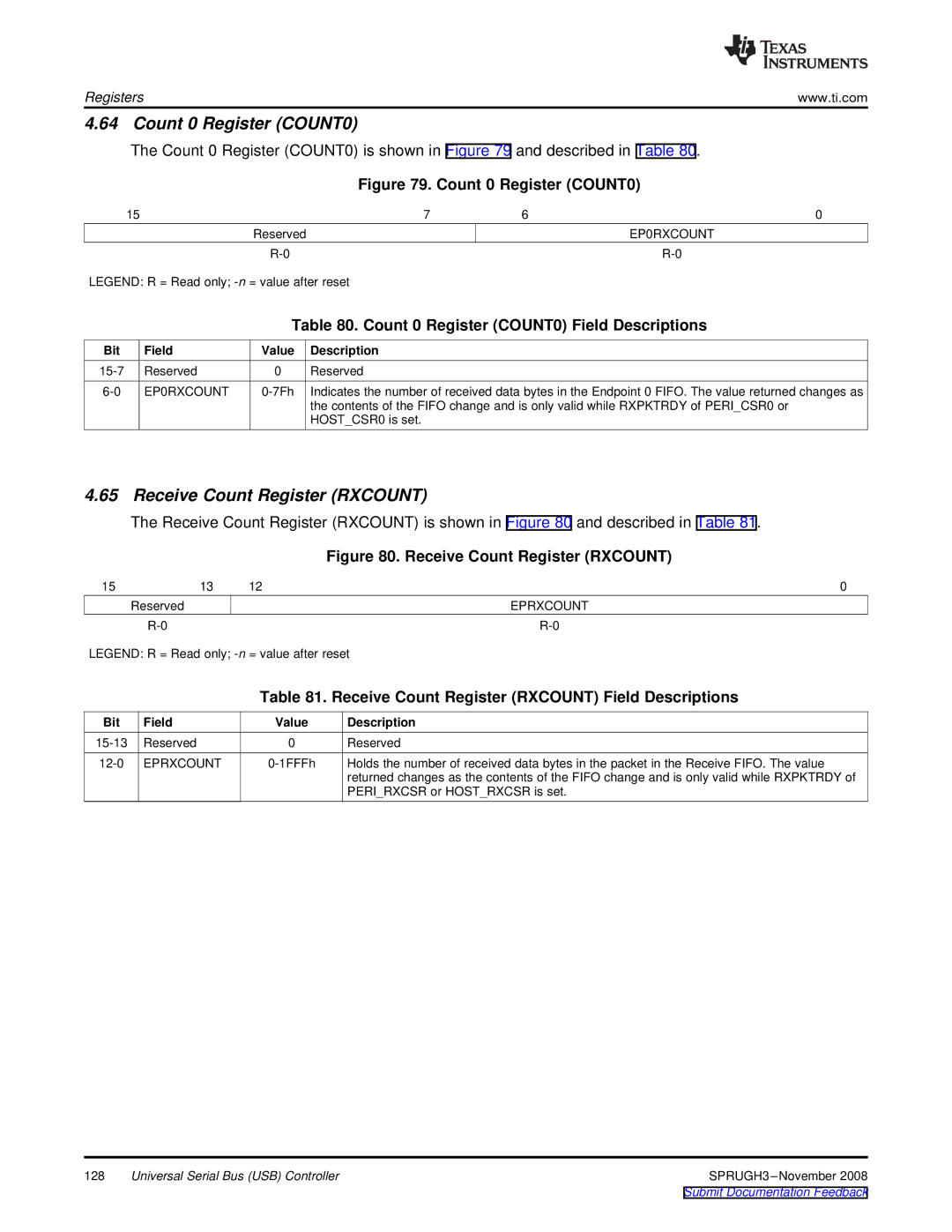

4.64 Count 0 Register (COUNT0)

The Count 0 Register (COUNT0) is shown in Figure 79 and described in Table 80.

Figure 79. Count 0 Register (COUNT0)

15 | 7 | 6 | 0 |

| Reserved |

| EP0RXCOUNT |

|

|

LEGEND: R = Read only;

Table 80. Count 0 Register (COUNT0) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

EP0RXCOUNT |

| Indicates the number of received data bytes in the Endpoint 0 FIFO. The value returned changes as | |

|

|

| the contents of the FIFO change and is only valid while RXPKTRDY of PERI_CSR0 or |

|

|

| HOST_CSR0 is set. |

4.65 Receive Count Register (RXCOUNT)

The Receive Count Register (RXCOUNT) is shown in Figure 80 and described in Table 81.

|

|

| Figure 80. Receive Count Register (RXCOUNT) |

15 | 13 | 12 | 0 |

| Reserved |

| EPRXCOUNT |

|

|

LEGEND: R = Read only;

Table 81. Receive Count Register (RXCOUNT) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

EPRXCOUNT | Holds the number of received data bytes in the packet in the Receive FIFO. The value | ||

|

|

| returned changes as the contents of the FIFO change and is only valid while RXPKTRDY of |

|

|

| PERI_RXCSR or HOST_RXCSR is set. |

128 | Universal Serial Bus (USB) Controller |