Registers | www.ti.com |

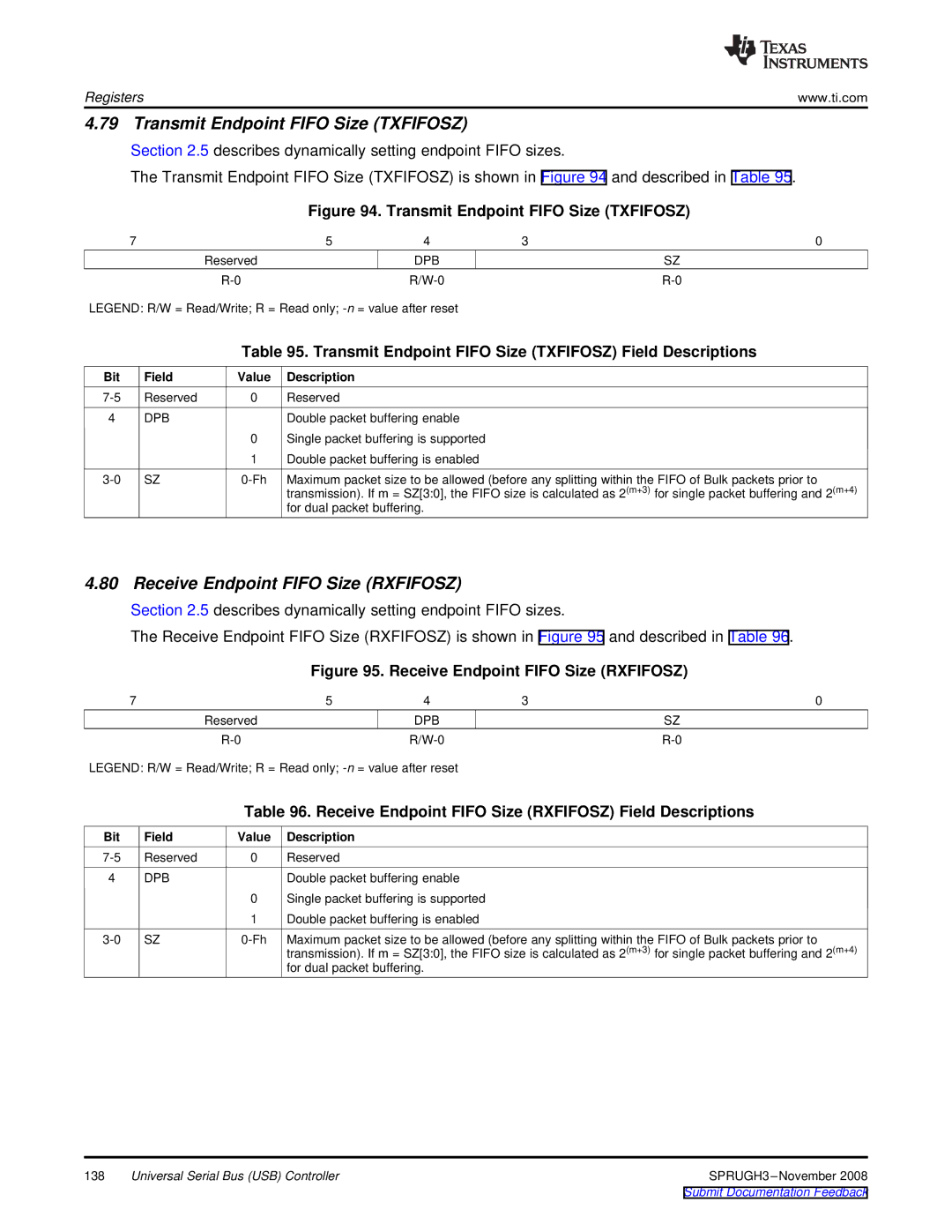

4.79 Transmit Endpoint FIFO Size (TXFIFOSZ)

Section 2.5 describes dynamically setting endpoint FIFO sizes.

The Transmit Endpoint FIFO Size (TXFIFOSZ) is shown in Figure 94 and described in Table 95.

Figure 94. Transmit Endpoint FIFO Size (TXFIFOSZ)

7 | 5 | 4 | 3 | 0 |

Reserved |

| DPB |

| SZ |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 95. Transmit Endpoint FIFO Size (TXFIFOSZ) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

4 | DPB |

| Double packet buffering enable |

|

| 0 | Single packet buffering is supported |

|

| 1 | Double packet buffering is enabled |

SZ | Maximum packet size to be allowed (before any splitting within the FIFO of Bulk packets prior to | ||

|

|

| transmission). If m = SZ[3:0], the FIFO size is calculated as 2(m+3) for single packet buffering and 2(m+4) |

for dual packet buffering.

4.80 Receive Endpoint FIFO Size (RXFIFOSZ)

Section 2.5 describes dynamically setting endpoint FIFO sizes.

The Receive Endpoint FIFO Size (RXFIFOSZ) is shown in Figure 95 and described in Table 96.

Figure 95. Receive Endpoint FIFO Size (RXFIFOSZ)

7 | 5 | 4 | 3 | 0 |

Reserved |

| DPB |

| SZ |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 96. Receive Endpoint FIFO Size (RXFIFOSZ) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

4 | DPB |

| Double packet buffering enable |

|

| 0 | Single packet buffering is supported |

|

| 1 | Double packet buffering is enabled |

SZ | Maximum packet size to be allowed (before any splitting within the FIFO of Bulk packets prior to | ||

|

|

| transmission). If m = SZ[3:0], the FIFO size is calculated as 2(m+3) for single packet buffering and 2(m+4) |

for dual packet buffering.

138 | Universal Serial Bus (USB) Controller |