www.ti.com | Registers |

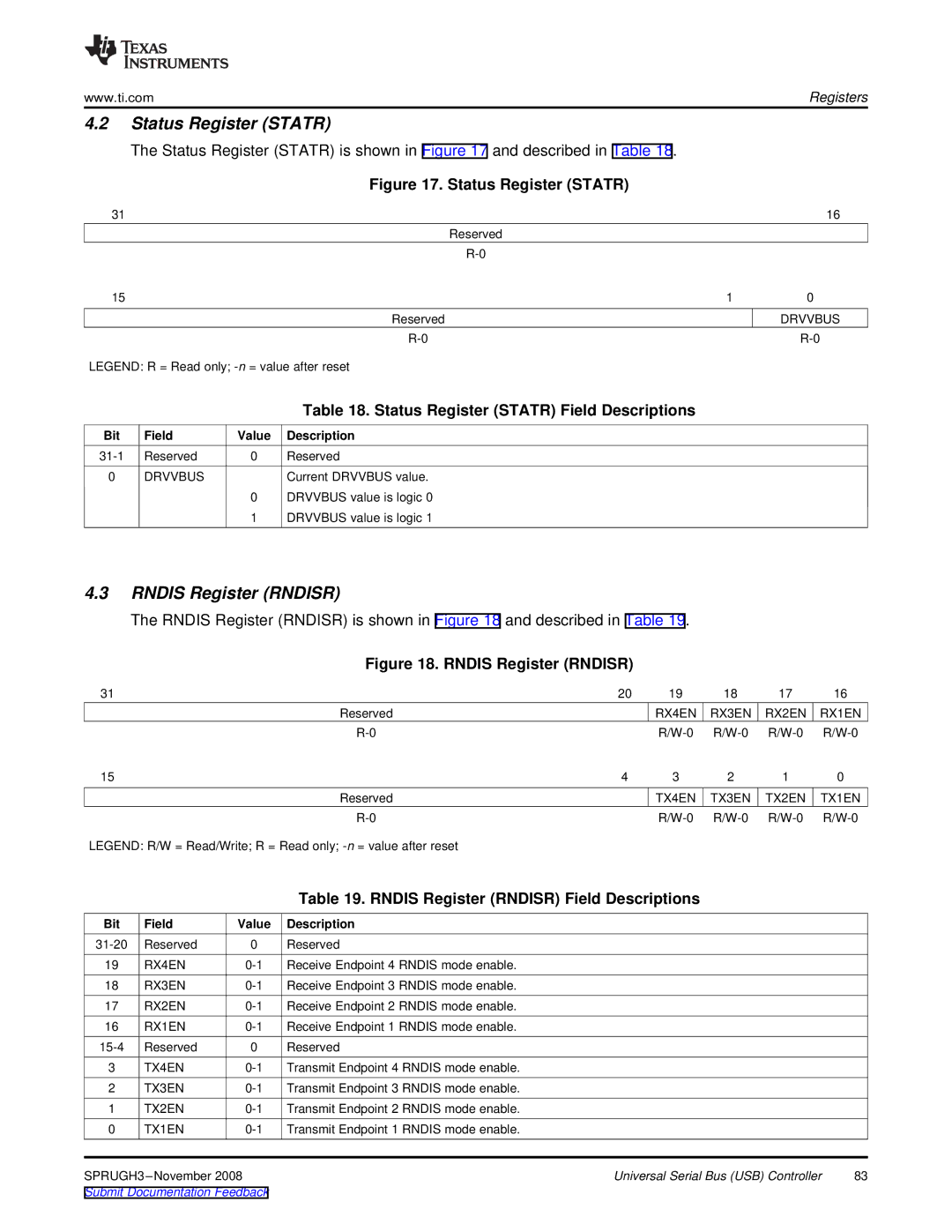

4.2Status Register (STATR)

The Status Register (STATR) is shown in Figure 17 and described in Table 18.

Figure 17. Status Register (STATR)

31 |

|

|

| 16 |

|

|

| Reserved |

|

|

|

|

| |

15 |

|

| 1 | 0 |

|

|

| Reserved | DRVVBUS |

|

|

| ||

LEGEND: R = Read only; |

| |||

|

|

| Table 18. Status Register (STATR) Field Descriptions |

|

Bit | Field | Value | Description |

|

Reserved | 0 | Reserved |

| |

0 | DRVVBUS |

| Current DRVVBUS value. |

|

|

| 0 | DRVVBUS value is logic 0 |

|

|

| 1 | DRVVBUS value is logic 1 |

|

4.3RNDIS Register (RNDISR)

The RNDIS Register (RNDISR) is shown in Figure 18 and described in Table 19.

Figure 18. RNDIS Register (RNDISR)

31 | 20 | 19 | 18 | 17 | 16 |

Reserved |

| RX4EN | RX3EN | RX2EN | RX1EN |

| |||||

15 | 4 | 3 | 2 | 1 | 0 |

Reserved |

| TX4EN | TX3EN | TX2EN | TX1EN |

| |||||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

|

|

|

|

|

| Table 19. RNDIS Register (RNDISR) Field Descriptions |

|

Bit | Field | Value | Description |

|

Reserved | 0 | Reserved |

| |

19 | RX4EN | Receive Endpoint 4 RNDIS mode enable. |

| |

18 | RX3EN | Receive Endpoint 3 RNDIS mode enable. |

| |

17 | RX2EN | Receive Endpoint 2 RNDIS mode enable. |

| |

16 | RX1EN | Receive Endpoint 1 RNDIS mode enable. |

| |

Reserved | 0 | Reserved |

| |

3 | TX4EN | Transmit Endpoint 4 RNDIS mode enable. |

| |

2 | TX3EN | Transmit Endpoint 3 RNDIS mode enable. |

| |

1 | TX2EN | Transmit Endpoint 2 RNDIS mode enable. |

| |

0 | TX1EN | Transmit Endpoint 1 RNDIS mode enable. |

| |

Universal Serial Bus (USB) Controller | 83 | |||

Submit Documentation Feedback |

|

| ||