www.ti.com | Registers |

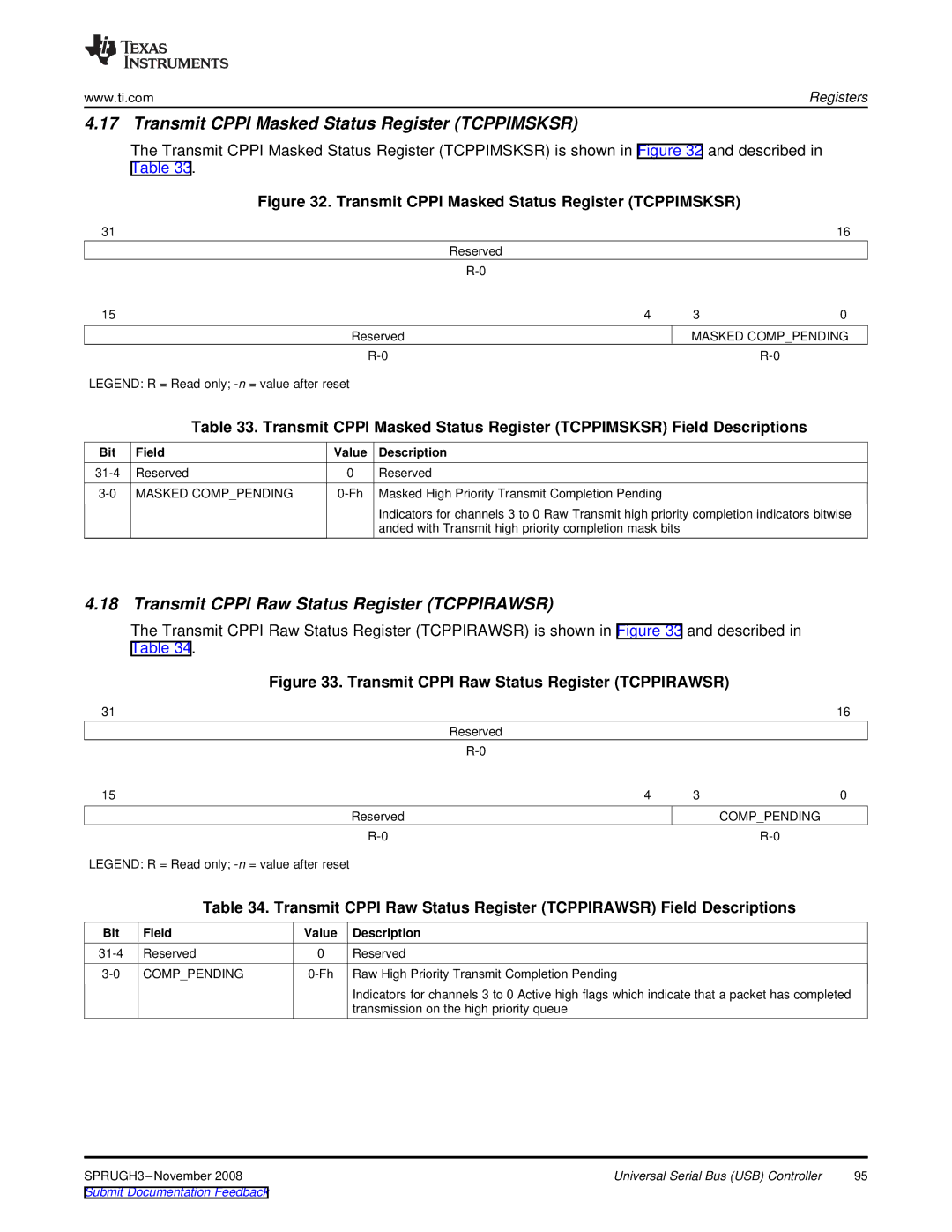

4.17 Transmit CPPI Masked Status Register (TCPPIMSKSR)

The Transmit CPPI Masked Status Register (TCPPIMSKSR) is shown in Figure 32 and described in Table 33.

Figure 32. Transmit CPPI Masked Status Register (TCPPIMSKSR)

31 |

|

|

|

| 16 |

|

|

| Reserved |

|

|

|

|

|

|

| |

15 |

|

| 4 | 3 | 0 |

|

| Reserved | MASKED COMP_PENDING | ||

|

|

|

| ||

LEGEND: R = Read only; |

|

|

| ||

| Table 33. Transmit CPPI Masked Status Register (TCPPIMSKSR) Field Descriptions |

| |||

Bit | Field | Value | Description |

|

|

Reserved | 0 | Reserved |

|

| |

MASKED COMP_PENDING | Masked High Priority Transmit Completion Pending |

|

| ||

|

|

| Indicators for channels 3 to 0 Raw Transmit high priority completion indicators bitwise | ||

|

|

| anded with Transmit high priority completion mask bits |

|

|

4.18 Transmit CPPI Raw Status Register (TCPPIRAWSR)

The Transmit CPPI Raw Status Register (TCPPIRAWSR) is shown in Figure 33 and described in Table 34.

Figure 33. Transmit CPPI Raw Status Register (TCPPIRAWSR)

31 |

|

|

|

| 16 |

|

|

| Reserved |

|

|

|

|

|

|

| |

15 |

|

| 4 | 3 | 0 |

|

|

| Reserved |

| COMP_PENDING |

|

|

|

| ||

LEGEND: R = Read only; |

|

|

| ||

| Table 34. Transmit CPPI Raw Status Register (TCPPIRAWSR) Field Descriptions | ||||

Bit | Field | Value | Description |

|

|

Reserved | 0 | Reserved |

|

| |

COMP_PENDING | Raw High Priority Transmit Completion Pending |

|

| ||

|

|

| Indicators for channels 3 to 0 Active high flags which indicate that a packet has completed | ||

|

|

| transmission on the high priority queue |

|

|

Universal Serial Bus (USB) Controller | 95 | |

Submit Documentation Feedback |

|

|