www.ti.com | Registers |

4.62 Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR)

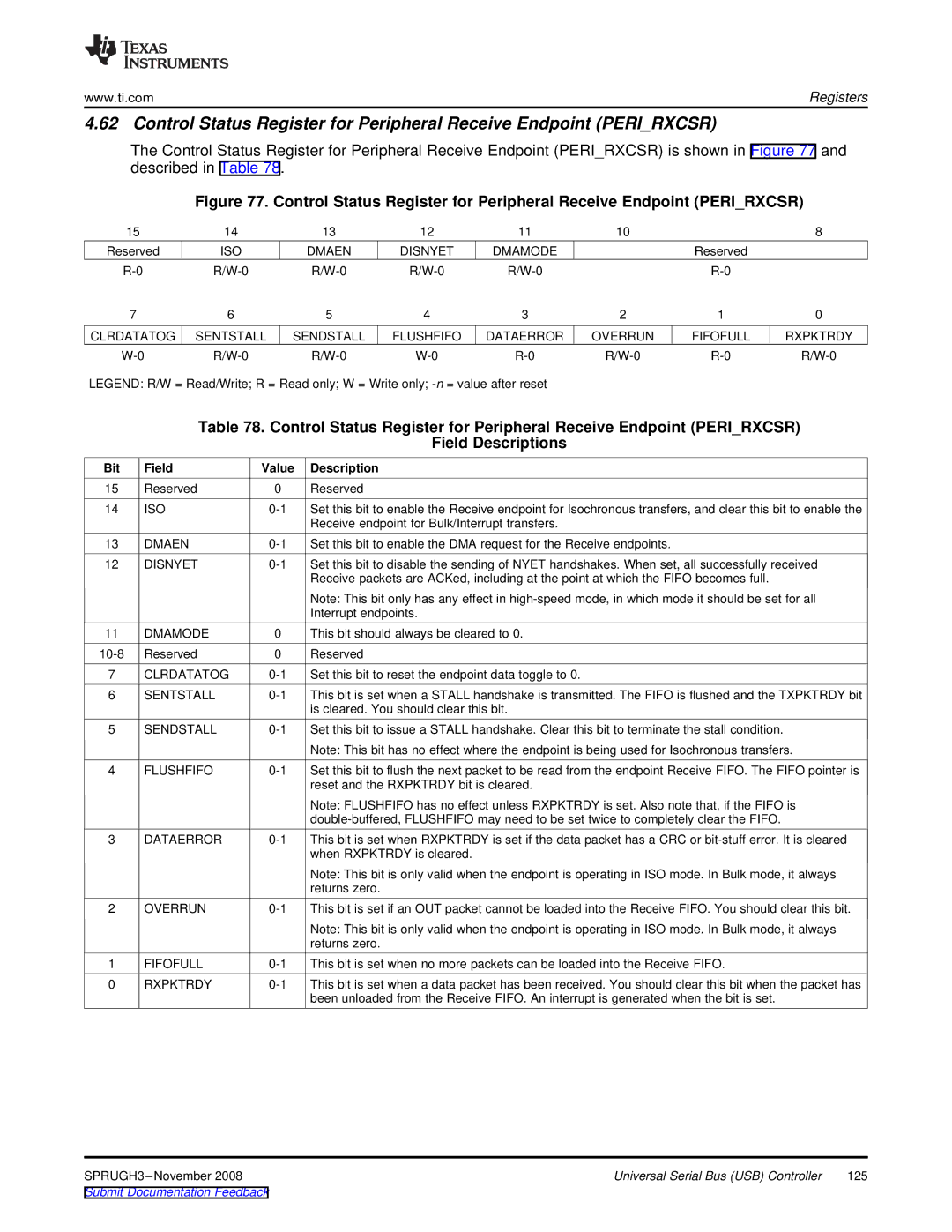

The Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR) is shown in Figure 77 and described in Table 78.

Figure 77. Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR)

15 |

| 14 |

|

| 13 | 12 | 11 | 10 |

| 8 |

Reserved | ISO |

|

| DMAEN | DISNYET | DMAMODE |

| Reserved |

| |

|

|

|

|

| ||||||

7 |

| 6 |

|

| 5 | 4 | 3 | 2 | 1 | 0 |

CLRDATATOG | SENTSTALL | SENDSTALL | FLUSHFIFO | DATAERROR | OVERRUN | FIFOFULL | RXPKTRDY | |||

|

| |||||||||

LEGEND: R/W = Read/Write; R = Read only; W = Write only; |

|

|

| |||||||

|

| Table 78. Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR) | ||||||||

|

|

|

|

|

| Field Descriptions |

|

|

| |

Bit | Field |

| Value | Description |

|

|

|

|

| |

15 | Reserved |

| 0 | Reserved |

|

|

|

|

| |

14 | ISO |

|

| Set this bit to enable the Receive endpoint for Isochronous transfers, and clear this bit to enable the | ||||||

|

|

|

|

| Receive endpoint for Bulk/Interrupt transfers. |

|

|

| ||

13 | DMAEN |

|

| Set this bit to enable the DMA request for the Receive endpoints. |

|

| ||||

12 | DISNYET |

| Set this bit to disable the sending of NYET handshakes. When set, all successfully received | |||||||

|

|

|

|

| Receive packets are ACKed, including at the point at which the FIFO becomes full. |

| ||||

|

|

|

|

| Note: This bit only has any effect in | |||||

|

|

|

|

| Interrupt endpoints. |

|

|

|

| |

11 | DMAMODE |

| 0 | This bit should always be cleared to 0. |

|

|

| |||

Reserved |

| 0 | Reserved |

|

|

|

|

| ||

7 | CLRDATATOG |

| Set this bit to reset the endpoint data toggle to 0. |

|

|

| ||||

6 | SENTSTALL |

| This bit is set when a STALL handshake is transmitted. The FIFO is flushed and the TXPKTRDY bit | |||||||

|

|

|

|

| is cleared. You should clear this bit. |

|

|

| ||

5 | SENDSTALL |

| Set this bit to issue a STALL handshake. Clear this bit to terminate the stall condition. |

| ||||||

|

|

|

|

| Note: This bit has no effect where the endpoint is being used for Isochronous transfers. | |||||

4 | FLUSHFIFO |

| Set this bit to flush the next packet to be read from the endpoint Receive FIFO. The FIFO pointer is | |||||||

|

|

|

|

| reset and the RXPKTRDY bit is cleared. |

|

|

| ||

|

|

|

|

| Note: FLUSHFIFO has no effect unless RXPKTRDY is set. Also note that, if the FIFO is | |||||

|

|

|

|

|

| |||||

3 | DATAERROR |

| This bit is set when RXPKTRDY is set if the data packet has a CRC or | |||||||

|

|

|

|

| when RXPKTRDY is cleared. |

|

|

|

| |

|

|

|

|

| Note: This bit is only valid when the endpoint is operating in ISO mode. In Bulk mode, it always | |||||

|

|

|

|

| returns zero. |

|

|

|

|

|

2 | OVERRUN |

| This bit is set if an OUT packet cannot be loaded into the Receive FIFO. You should clear this bit. | |||||||

|

|

|

|

| Note: This bit is only valid when the endpoint is operating in ISO mode. In Bulk mode, it always | |||||

|

|

|

|

| returns zero. |

|

|

|

|

|

1 | FIFOFULL |

| This bit is set when no more packets can be loaded into the Receive FIFO. |

| ||||||

0 | RXPKTRDY |

| This bit is set when a data packet has been received. You should clear this bit when the packet has | |||||||

|

|

|

|

| been unloaded from the Receive FIFO. An interrupt is generated when the bit is set. |

| ||||

Universal Serial Bus (USB) Controller | 125 | |

Submit Documentation Feedback |

|

|