www.ti.com | Registers |

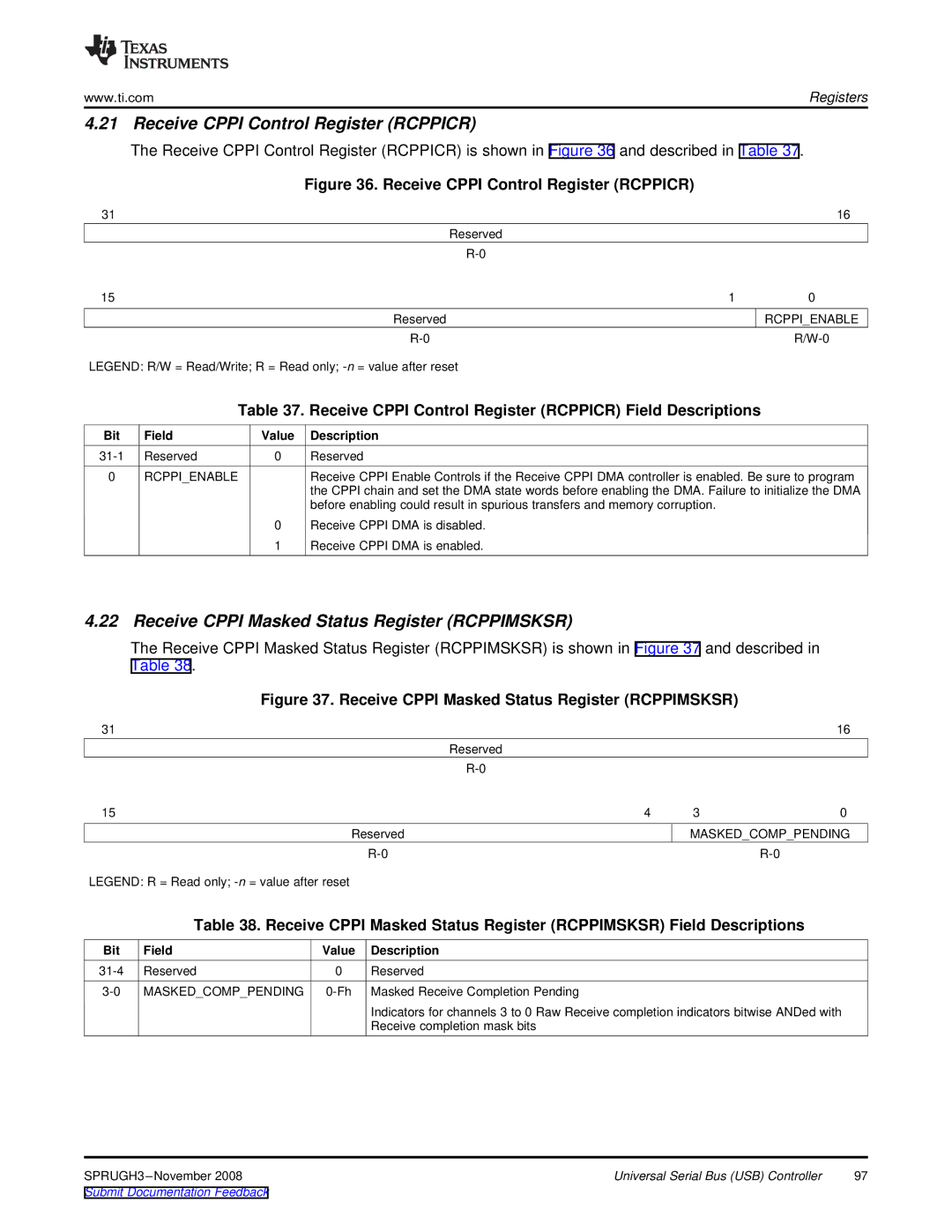

4.21 Receive CPPI Control Register (RCPPICR)

The Receive CPPI Control Register (RCPPICR) is shown in Figure 36 and described in Table 37.

Figure 36. Receive CPPI Control Register (RCPPICR)

31 |

|

|

| 16 |

|

|

| Reserved |

|

|

|

|

| |

15 |

|

| 1 | 0 |

|

|

| Reserved | RCPPI_ENABLE |

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

| |||

|

| Table 37. Receive CPPI Control Register (RCPPICR) Field Descriptions |

| |

Bit | Field | Value | Description |

|

Reserved | 0 | Reserved |

| |

0 | RCPPI_ENABLE | Receive CPPI Enable Controls if the Receive CPPI DMA controller is enabled. Be sure to program | ||

|

|

| the CPPI chain and set the DMA state words before enabling the DMA. Failure to initialize the DMA | |

|

|

| before enabling could result in spurious transfers and memory corruption. |

|

|

| 0 | Receive CPPI DMA is disabled. |

|

|

| 1 | Receive CPPI DMA is enabled. |

|

4.22 Receive CPPI Masked Status Register (RCPPIMSKSR)

The Receive CPPI Masked Status Register (RCPPIMSKSR) is shown in Figure 37 and described in Table 38.

Figure 37. Receive CPPI Masked Status Register (RCPPIMSKSR)

31 |

|

|

|

| 16 |

|

|

| Reserved |

|

|

|

|

|

|

| |

15 |

|

| 4 | 3 | 0 |

|

| Reserved | MASKED_COMP_PENDING | ||

|

|

|

| ||

LEGEND: R = Read only; |

|

|

| ||

| Table 38. Receive CPPI Masked Status Register (RCPPIMSKSR) Field Descriptions |

| |||

Bit | Field | Value | Description |

|

|

Reserved | 0 | Reserved |

|

| |

MASKED_COMP_PENDING | Masked Receive Completion Pending |

|

| ||

|

|

| Indicators for channels 3 to 0 Raw Receive completion indicators bitwise ANDed with | ||

|

|

| Receive completion mask bits |

|

|

Universal Serial Bus (USB) Controller | 97 | |

Submit Documentation Feedback |

|

|