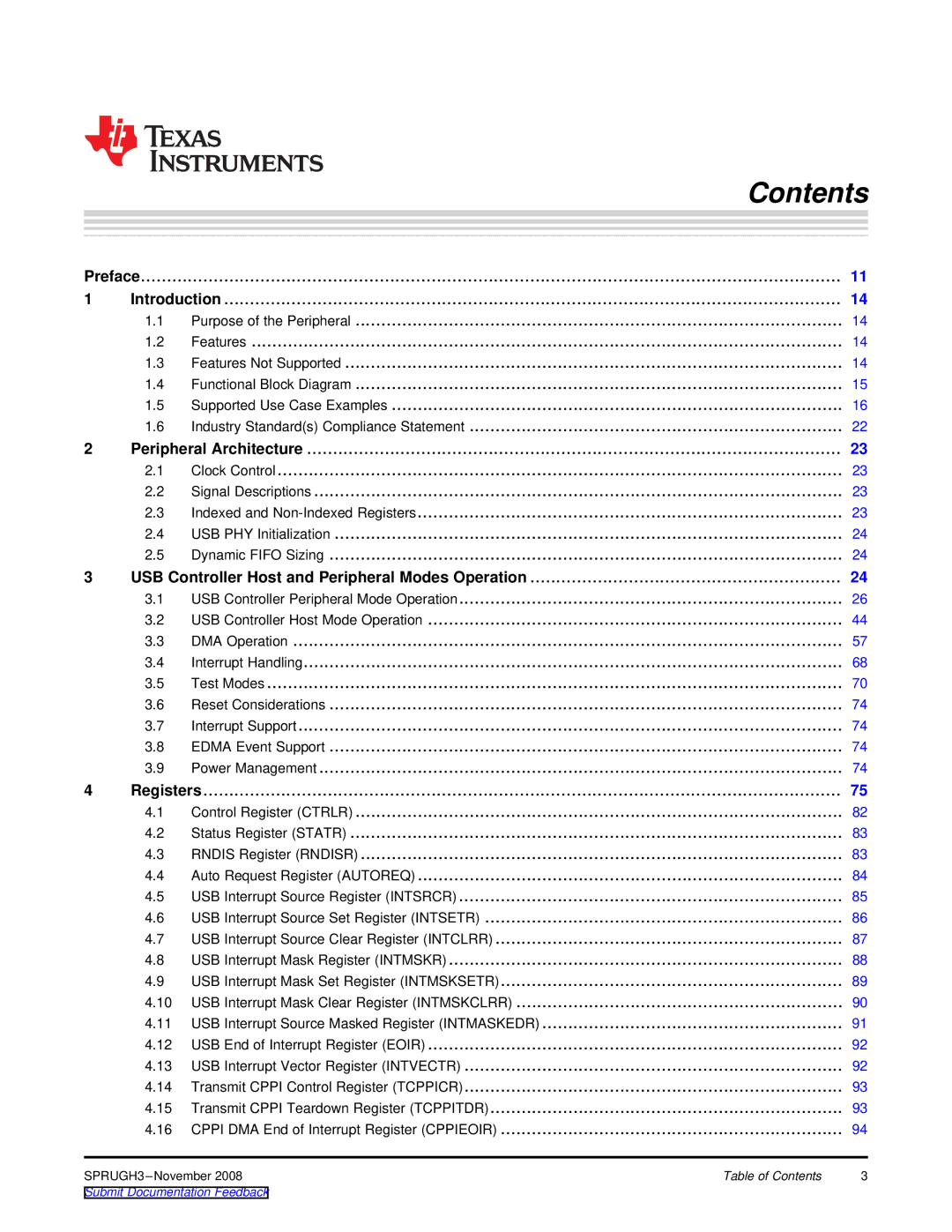

Contents

Preface |

| 11 | ||

1 | Introduction | 14 | ||

| 1.1 | Purpose of the Peripheral | 14 | |

| 1.2 | Features | 14 | |

| 1.3 | Features Not Supported | 14 | |

| 1.4 | Functional Block Diagram | 15 | |

| 1.5 | Supported Use Case Examples | 16 | |

| 1.6 | Industry Standard(s) Compliance Statement | 22 | |

2 | Peripheral Architecture | 23 | ||

| 2.1 | Clock Control | 23 | |

| 2.2 | Signal Descriptions | 23 | |

| 2.3 | Indexed and | 23 | |

| 2.4 | USB PHY Initialization | 24 | |

| 2.5 | Dynamic FIFO Sizing | 24 | |

3 | USB Controller Host and Peripheral Modes Operation | 24 | ||

| 3.1 | USB Controller Peripheral Mode Operation | 26 | |

| 3.2 | USB Controller Host Mode Operation | 44 | |

| 3.3 | DMA Operation | 57 | |

| 3.4 | Interrupt Handling | 68 | |

| 3.5 | Test Modes | 70 | |

| 3.6 | Reset Considerations | 74 | |

| 3.7 | Interrupt Support | 74 | |

| 3.8 | EDMA Event Support | 74 | |

| 3.9 | Power Management | 74 | |

4 | Registers | 75 | ||

| 4.1 | Control Register (CTRLR) | 82 | |

| 4.2 | Status Register (STATR) | 83 | |

| 4.3 | RNDIS Register (RNDISR) | 83 | |

| 4.4 | Auto Request Register (AUTOREQ) | 84 | |

| 4.5 | USB Interrupt Source Register (INTSRCR) | 85 | |

| 4.6 | USB Interrupt Source Set Register (INTSETR) | 86 | |

| 4.7 | USB Interrupt Source Clear Register (INTCLRR) | 87 | |

| 4.8 | USB Interrupt Mask Register (INTMSKR) | 88 | |

| 4.9 | USB Interrupt Mask Set Register (INTMSKSETR) | 89 | |

| 4.10 | USB Interrupt Mask Clear Register (INTMSKCLRR) | 90 | |

| 4.11 | USB Interrupt Source Masked Register (INTMASKEDR) | 91 | |

| 4.12 | USB End of Interrupt Register (EOIR) | 92 | |

| 4.13 | USB Interrupt Vector Register (INTVECTR) | 92 | |

| 4.14 | Transmit CPPI Control Register (TCPPICR) | 93 | |

| 4.15 | Transmit CPPI Teardown Register (TCPPITDR) | 93 | |

| 4.16 | CPPI DMA End of Interrupt Register (CPPIEOIR) | 94 | |

Table of Contents | 3 | |||