www.ti.com | Registers |

4.51 Interrupt Register for Common USB Interrupts (INTRUSB)

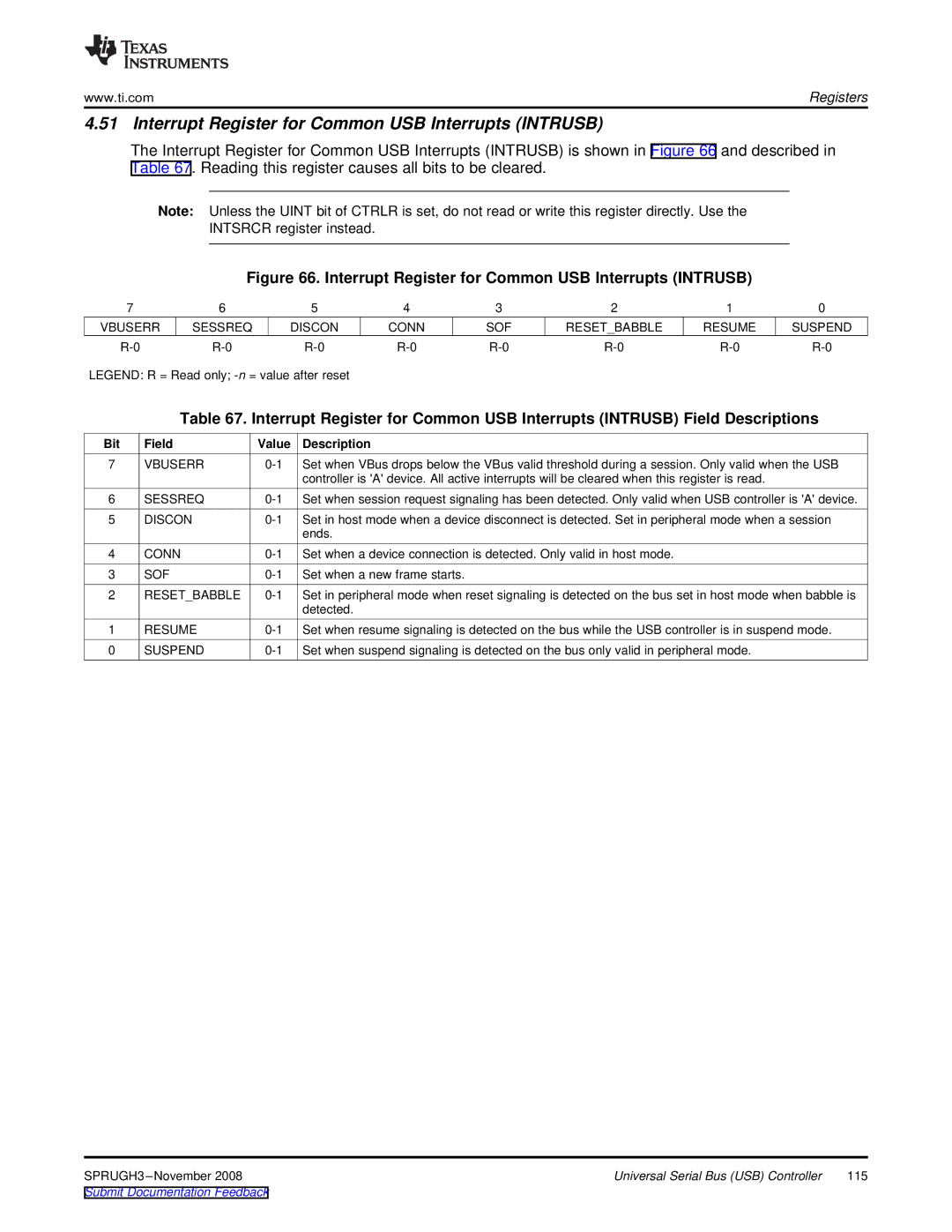

The Interrupt Register for Common USB Interrupts (INTRUSB) is shown in Figure 66 and described in Table 67. Reading this register causes all bits to be cleared.

Note: Unless the UINT bit of CTRLR is set, do not read or write this register directly. Use the INTSRCR register instead.

Figure 66. Interrupt Register for Common USB Interrupts (INTRUSB)

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

VBUSERR | SESSREQ | DISCON | CONN | SOF | RESET_BABBLE | RESUME | SUSPEND |

LEGEND: R = Read only;

Table 67. Interrupt Register for Common USB Interrupts (INTRUSB) Field Descriptions

Bit | Field | Value | Description |

7 | VBUSERR | Set when VBus drops below the VBus valid threshold during a session. Only valid when the USB | |

|

|

| controller is 'A' device. All active interrupts will be cleared when this register is read. |

6 | SESSREQ | Set when session request signaling has been detected. Only valid when USB controller is 'A' device. | |

5 | DISCON | Set in host mode when a device disconnect is detected. Set in peripheral mode when a session | |

|

|

| ends. |

4 | CONN | Set when a device connection is detected. Only valid in host mode. | |

3 | SOF | Set when a new frame starts. | |

2 | RESET_BABBLE | Set in peripheral mode when reset signaling is detected on the bus set in host mode when babble is | |

|

|

| detected. |

1 | RESUME | Set when resume signaling is detected on the bus while the USB controller is in suspend mode. | |

0 | SUSPEND | Set when suspend signaling is detected on the bus only valid in peripheral mode. |

Universal Serial Bus (USB) Controller | 115 | |

Submit Documentation Feedback |

|

|