www.ti.com | Registers |

4Registers

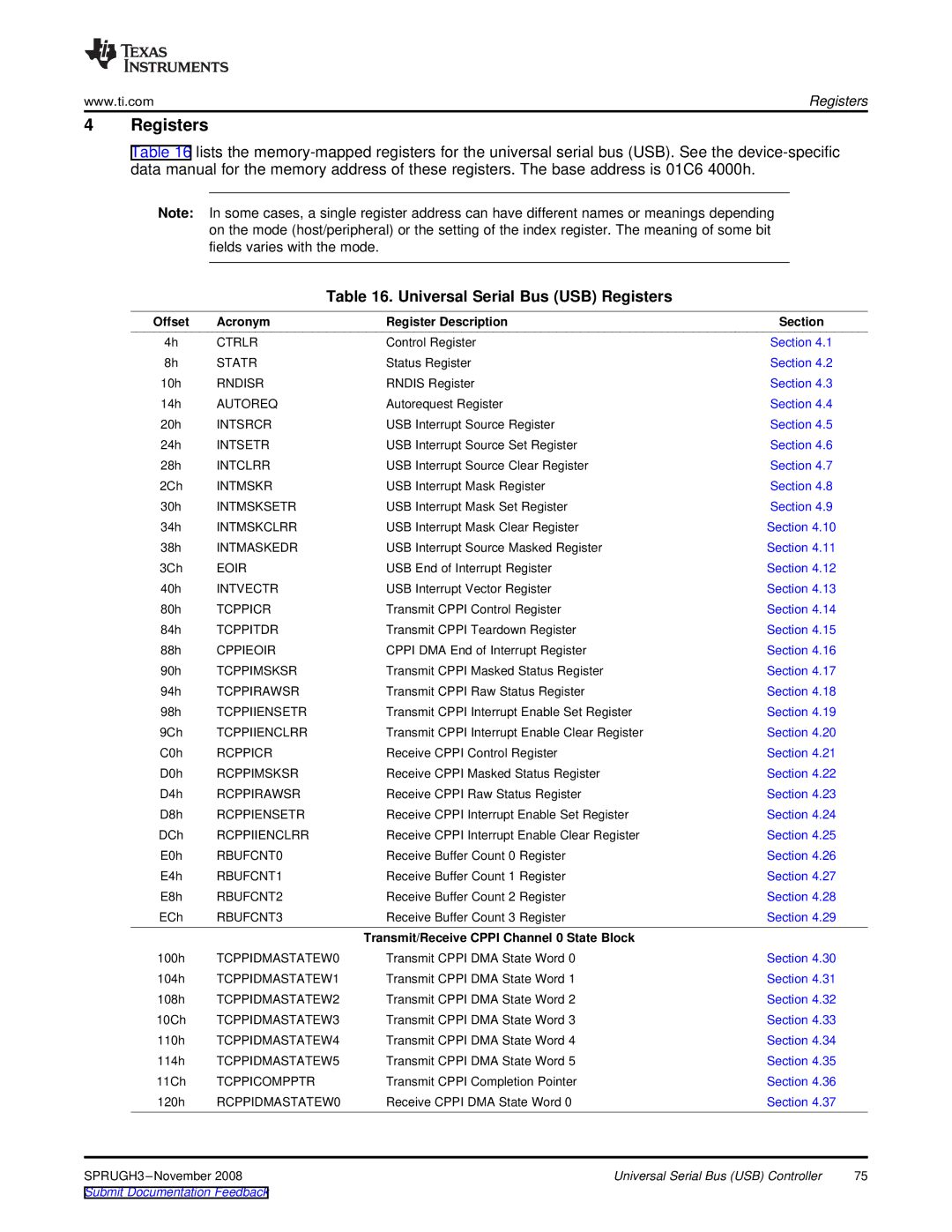

Table 16 lists the

Note: In some cases, a single register address can have different names or meanings depending on the mode (host/peripheral) or the setting of the index register. The meaning of some bit fields varies with the mode.

Table 16. Universal Serial Bus (USB) Registers

Offset | Acronym | Register Description | Section |

4h | CTRLR | Control Register | Section 4.1 |

8h | STATR | Status Register | Section 4.2 |

10h | RNDISR | RNDIS Register | Section 4.3 |

14h | AUTOREQ | Autorequest Register | Section 4.4 |

20h | INTSRCR | USB Interrupt Source Register | Section 4.5 |

24h | INTSETR | USB Interrupt Source Set Register | Section 4.6 |

28h | INTCLRR | USB Interrupt Source Clear Register | Section 4.7 |

2Ch | INTMSKR | USB Interrupt Mask Register | Section 4.8 |

30h | INTMSKSETR | USB Interrupt Mask Set Register | Section 4.9 |

34h | INTMSKCLRR | USB Interrupt Mask Clear Register | Section 4.10 |

38h | INTMASKEDR | USB Interrupt Source Masked Register | Section 4.11 |

3Ch | EOIR | USB End of Interrupt Register | Section 4.12 |

40h | INTVECTR | USB Interrupt Vector Register | Section 4.13 |

80h | TCPPICR | Transmit CPPI Control Register | Section 4.14 |

84h | TCPPITDR | Transmit CPPI Teardown Register | Section 4.15 |

88h | CPPIEOIR | CPPI DMA End of Interrupt Register | Section 4.16 |

90h | TCPPIMSKSR | Transmit CPPI Masked Status Register | Section 4.17 |

94h | TCPPIRAWSR | Transmit CPPI Raw Status Register | Section 4.18 |

98h | TCPPIIENSETR | Transmit CPPI Interrupt Enable Set Register | Section 4.19 |

9Ch | TCPPIIENCLRR | Transmit CPPI Interrupt Enable Clear Register | Section 4.20 |

C0h | RCPPICR | Receive CPPI Control Register | Section 4.21 |

D0h | RCPPIMSKSR | Receive CPPI Masked Status Register | Section 4.22 |

D4h | RCPPIRAWSR | Receive CPPI Raw Status Register | Section 4.23 |

D8h | RCPPIENSETR | Receive CPPI Interrupt Enable Set Register | Section 4.24 |

DCh | RCPPIIENCLRR | Receive CPPI Interrupt Enable Clear Register | Section 4.25 |

E0h | RBUFCNT0 | Receive Buffer Count 0 Register | Section 4.26 |

E4h | RBUFCNT1 | Receive Buffer Count 1 Register | Section 4.27 |

E8h | RBUFCNT2 | Receive Buffer Count 2 Register | Section 4.28 |

ECh | RBUFCNT3 | Receive Buffer Count 3 Register | Section 4.29 |

|

| Transmit/Receive CPPI Channel 0 State Block |

|

100h | TCPPIDMASTATEW0 | Transmit CPPI DMA State Word 0 | Section 4.30 |

104h | TCPPIDMASTATEW1 | Transmit CPPI DMA State Word 1 | Section 4.31 |

108h | TCPPIDMASTATEW2 | Transmit CPPI DMA State Word 2 | Section 4.32 |

10Ch | TCPPIDMASTATEW3 | Transmit CPPI DMA State Word 3 | Section 4.33 |

110h | TCPPIDMASTATEW4 | Transmit CPPI DMA State Word 4 | Section 4.34 |

114h | TCPPIDMASTATEW5 | Transmit CPPI DMA State Word 5 | Section 4.35 |

11Ch | TCPPICOMPPTR | Transmit CPPI Completion Pointer | Section 4.36 |

120h | RCPPIDMASTATEW0 | Receive CPPI DMA State Word 0 | Section 4.37 |

Universal Serial Bus (USB) Controller | 75 | |

Submit Documentation Feedback |

|

|