www.ti.comRegisters

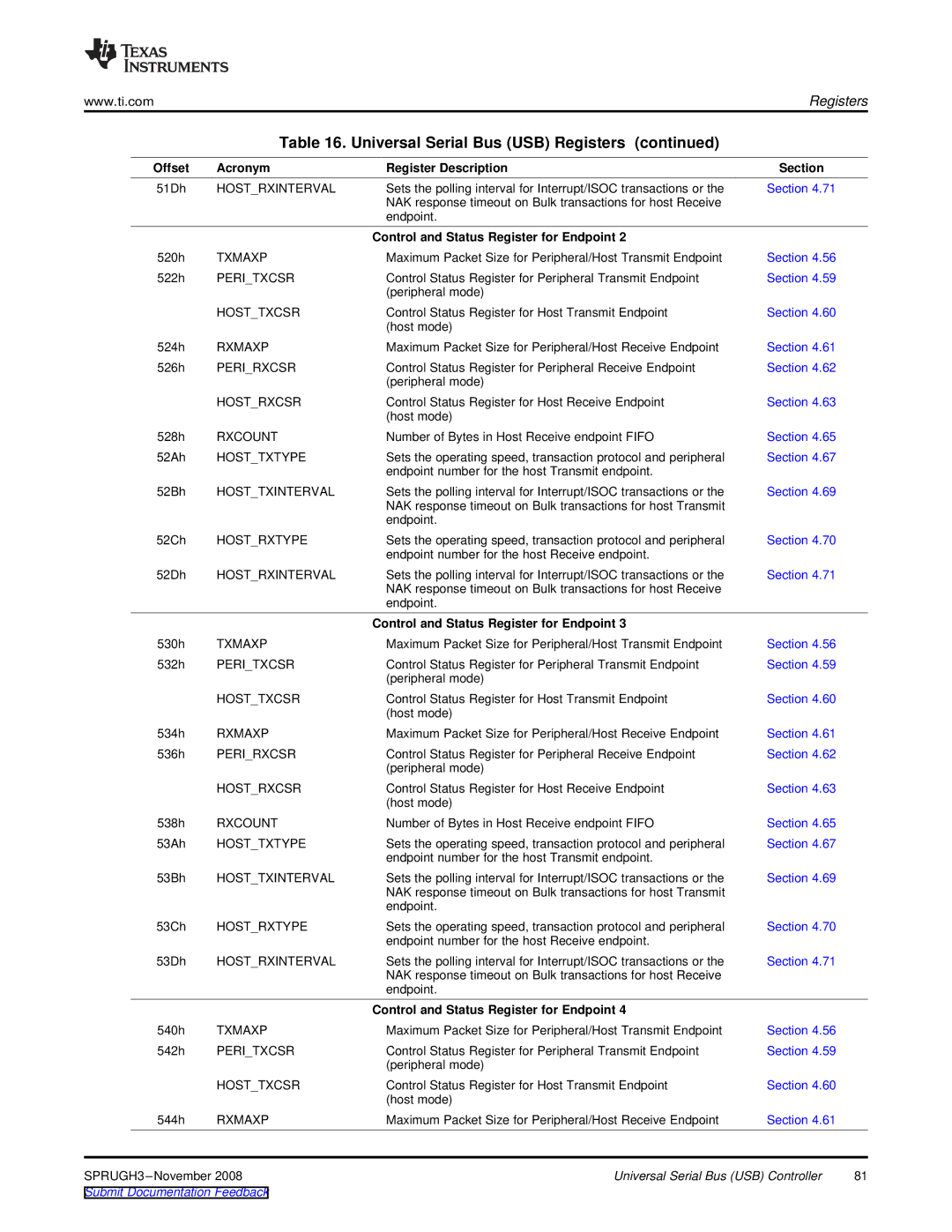

Table 16. Universal Serial Bus (USB) Registers (continued)

Offset | Acronym | Register Description | Section |

|

51Dh | HOST_RXINTERVAL | Sets the polling interval for Interrupt/ISOC transactions or the | Section 4.71 |

|

|

| NAK response timeout on Bulk transactions for host Receive |

|

|

|

| endpoint. |

|

|

|

| Control and Status Register for Endpoint 2 |

|

|

520h | TXMAXP | Maximum Packet Size for Peripheral/Host Transmit Endpoint | Section 4.56 |

|

522h | PERI_TXCSR | Control Status Register for Peripheral Transmit Endpoint | Section 4.59 |

|

|

| (peripheral mode) |

|

|

| HOST_TXCSR | Control Status Register for Host Transmit Endpoint | Section 4.60 |

|

|

| (host mode) |

|

|

524h | RXMAXP | Maximum Packet Size for Peripheral/Host Receive Endpoint | Section 4.61 |

|

526h | PERI_RXCSR | Control Status Register for Peripheral Receive Endpoint | Section 4.62 |

|

|

| (peripheral mode) |

|

|

| HOST_RXCSR | Control Status Register for Host Receive Endpoint | Section 4.63 |

|

|

| (host mode) |

|

|

528h | RXCOUNT | Number of Bytes in Host Receive endpoint FIFO | Section 4.65 |

|

52Ah | HOST_TXTYPE | Sets the operating speed, transaction protocol and peripheral | Section 4.67 |

|

|

| endpoint number for the host Transmit endpoint. |

|

|

52Bh | HOST_TXINTERVAL | Sets the polling interval for Interrupt/ISOC transactions or the | Section 4.69 |

|

|

| NAK response timeout on Bulk transactions for host Transmit |

|

|

|

| endpoint. |

|

|

52Ch | HOST_RXTYPE | Sets the operating speed, transaction protocol and peripheral | Section 4.70 |

|

|

| endpoint number for the host Receive endpoint. |

|

|

52Dh | HOST_RXINTERVAL | Sets the polling interval for Interrupt/ISOC transactions or the | Section 4.71 |

|

|

| NAK response timeout on Bulk transactions for host Receive |

|

|

|

| endpoint. |

|

|

|

| Control and Status Register for Endpoint 3 |

|

|

530h | TXMAXP | Maximum Packet Size for Peripheral/Host Transmit Endpoint | Section 4.56 |

|

532h | PERI_TXCSR | Control Status Register for Peripheral Transmit Endpoint | Section 4.59 |

|

|

| (peripheral mode) |

|

|

| HOST_TXCSR | Control Status Register for Host Transmit Endpoint | Section 4.60 |

|

|

| (host mode) |

|

|

534h | RXMAXP | Maximum Packet Size for Peripheral/Host Receive Endpoint | Section 4.61 |

|

536h | PERI_RXCSR | Control Status Register for Peripheral Receive Endpoint | Section 4.62 |

|

|

| (peripheral mode) |

|

|

| HOST_RXCSR | Control Status Register for Host Receive Endpoint | Section 4.63 |

|

|

| (host mode) |

|

|

538h | RXCOUNT | Number of Bytes in Host Receive endpoint FIFO | Section 4.65 |

|

53Ah | HOST_TXTYPE | Sets the operating speed, transaction protocol and peripheral | Section 4.67 |

|

|

| endpoint number for the host Transmit endpoint. |

|

|

53Bh | HOST_TXINTERVAL | Sets the polling interval for Interrupt/ISOC transactions or the | Section 4.69 |

|

|

| NAK response timeout on Bulk transactions for host Transmit |

|

|

|

| endpoint. |

|

|

53Ch | HOST_RXTYPE | Sets the operating speed, transaction protocol and peripheral | Section 4.70 |

|

|

| endpoint number for the host Receive endpoint. |

|

|

53Dh | HOST_RXINTERVAL | Sets the polling interval for Interrupt/ISOC transactions or the | Section 4.71 |

|

|

| NAK response timeout on Bulk transactions for host Receive |

|

|

|

| endpoint. |

|

|

|

| Control and Status Register for Endpoint 4 |

|

|

540h | TXMAXP | Maximum Packet Size for Peripheral/Host Transmit Endpoint | Section 4.56 |

|

542h | PERI_TXCSR | Control Status Register for Peripheral Transmit Endpoint | Section 4.59 |

|

|

| (peripheral mode) |

|

|

| HOST_TXCSR | Control Status Register for Host Transmit Endpoint | Section 4.60 |

|

|

| (host mode) |

|

|

544h | RXMAXP | Maximum Packet Size for Peripheral/Host Receive Endpoint | Section 4.61 |

|

Universal Serial Bus (USB) Controller | 81 | |||

Submit Documentation Feedback |

|

|

| |