USB Controller Host and Peripheral Modes Operation | www.ti.com |

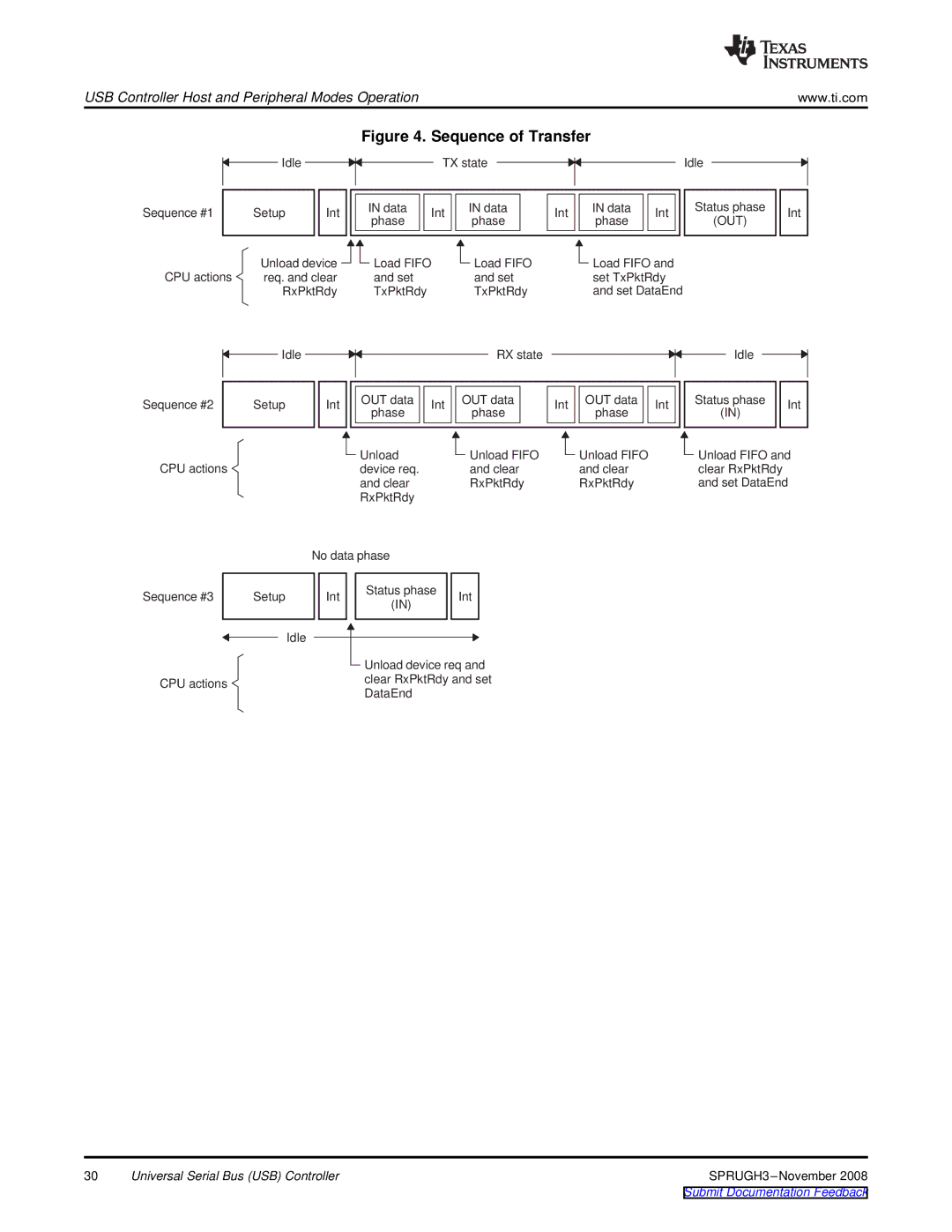

Figure 4. Sequence of Transfer

Idle

TX state ![]() Idle

Idle

Sequence #1 | Setup | Int |

|

|

|

Unload device ![]()

CPU actions ![]() req. and clear RxPktRdy

req. and clear RxPktRdy

Idle

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| IN data |

|

| Int |

|

| IN data |

| Int |

|

| IN data |

| Int |

|

| ||

|

| phase |

|

|

|

|

| phase |

|

|

| phase |

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

| Load FIFO |

|

|

| Load FIFO |

|

|

| Load FIFO and | ||||||||

|

|

|

|

|

|

|

| |||||||||||

|

|

|

|

|

|

|

| |||||||||||

|

| and set |

|

|

|

| and set |

|

|

| set TxPktRdy | |||||||

|

| TxPktRdy |

|

|

|

| TxPktRdy |

|

|

| and set DataEnd | |||||||

RX state

Status phase

(OUT)

Idle

Int

Sequence #2 | Setup |

|

|

CPU actions ![]()

Int

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| OUT data |

| Int |

| OUT data |

| Int | OUT data |

|

| Int |

| ||

|

| phase |

|

|

| phase |

| phase |

|

|

| ||||

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Unload |

|

|

|

| Unload FIFO |

|

| Unload FIFO |

|

| |||

|

|

|

|

|

|

|

|

|

| ||||||

|

|

|

|

|

|

|

|

|

| ||||||

|

| device req. |

|

|

|

| and clear |

|

| and clear |

|

| |||

|

| and clear |

|

|

|

| RxPktRdy |

|

| RxPktRdy |

|

| |||

|

| RxPktRdy |

|

|

|

|

|

|

|

|

|

|

|

|

|

Status phase |

| Int |

(IN) |

| |

|

| |

|

|

|

![]() Unload FIFO and clear RxPktRdy and set DataEnd

Unload FIFO and clear RxPktRdy and set DataEnd

No data phase

Sequence #3 | Setup |

|

|

Idle

CPU actions ![]()

Int |

|

|

| Status phase |

| Int |

|

|

|

| (IN) |

|

| ||

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

| Unload device req and | |||

|

|

|

| ||||

|

|

|

| ||||

|

|

|

| clear RxPktRdy and set | |||

|

|

|

| DataEnd |

|

|

|

30 | Universal Serial Bus (USB) Controller |