Registers | www.ti.com |

4.57 Control Status Register for Endpoint 0 in Peripheral Mode (PERI_CSR0)

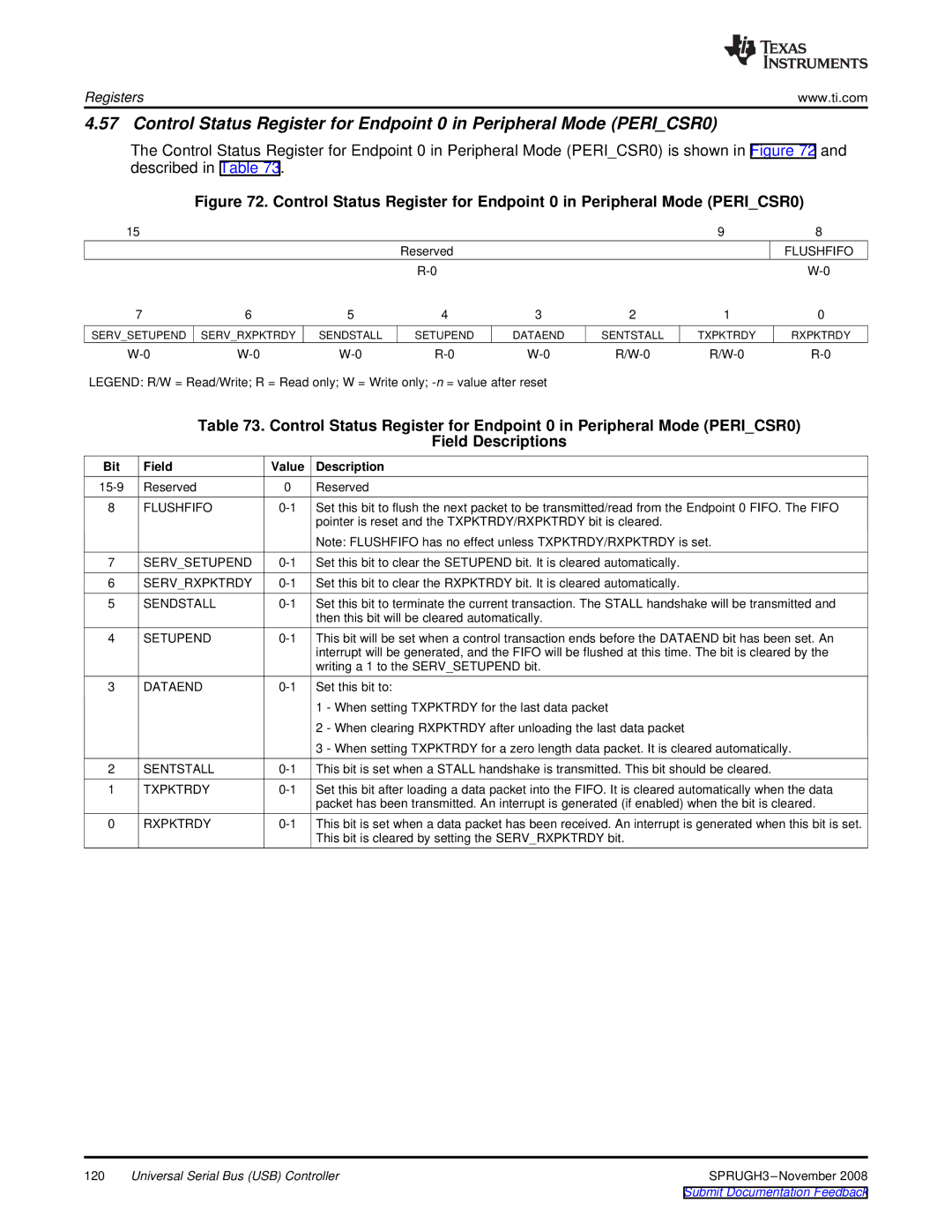

The Control Status Register for Endpoint 0 in Peripheral Mode (PERI_CSR0) is shown in Figure 72 and described in Table 73.

Figure 72. Control Status Register for Endpoint 0 in Peripheral Mode (PERI_CSR0)

15 |

|

|

|

|

| 9 | 8 |

|

|

| Reserved |

|

|

| FLUSHFIFO |

|

|

|

|

|

| ||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

SERV_SETUPEND | SERV_RXPKTRDY | SENDSTALL | SETUPEND | DATAEND | SENTSTALL | TXPKTRDY | RXPKTRDY |

LEGEND: R/W = Read/Write; R = Read only; W = Write only;

Table 73. Control Status Register for Endpoint 0 in Peripheral Mode (PERI_CSR0)

Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

8 | FLUSHFIFO | Set this bit to flush the next packet to be transmitted/read from the Endpoint 0 FIFO. The FIFO | |

|

|

| pointer is reset and the TXPKTRDY/RXPKTRDY bit is cleared. |

|

|

| Note: FLUSHFIFO has no effect unless TXPKTRDY/RXPKTRDY is set. |

7 | SERV_SETUPEND | Set this bit to clear the SETUPEND bit. It is cleared automatically. | |

6 | SERV_RXPKTRDY | Set this bit to clear the RXPKTRDY bit. It is cleared automatically. | |

5 | SENDSTALL | Set this bit to terminate the current transaction. The STALL handshake will be transmitted and | |

|

|

| then this bit will be cleared automatically. |

4 | SETUPEND | This bit will be set when a control transaction ends before the DATAEND bit has been set. An | |

|

|

| interrupt will be generated, and the FIFO will be flushed at this time. The bit is cleared by the |

|

|

| writing a 1 to the SERV_SETUPEND bit. |

3 | DATAEND | Set this bit to: | |

|

|

| 1 - When setting TXPKTRDY for the last data packet |

|

|

| 2 - When clearing RXPKTRDY after unloading the last data packet |

|

|

| 3 - When setting TXPKTRDY for a zero length data packet. It is cleared automatically. |

2 | SENTSTALL | This bit is set when a STALL handshake is transmitted. This bit should be cleared. | |

1 | TXPKTRDY | Set this bit after loading a data packet into the FIFO. It is cleared automatically when the data | |

|

|

| packet has been transmitted. An interrupt is generated (if enabled) when the bit is cleared. |

0 | RXPKTRDY | This bit is set when a data packet has been received. An interrupt is generated when this bit is set. | |

|

|

| This bit is cleared by setting the SERV_RXPKTRDY bit. |

120 | Universal Serial Bus (USB) Controller |