|

|

| www.ti.com |

|

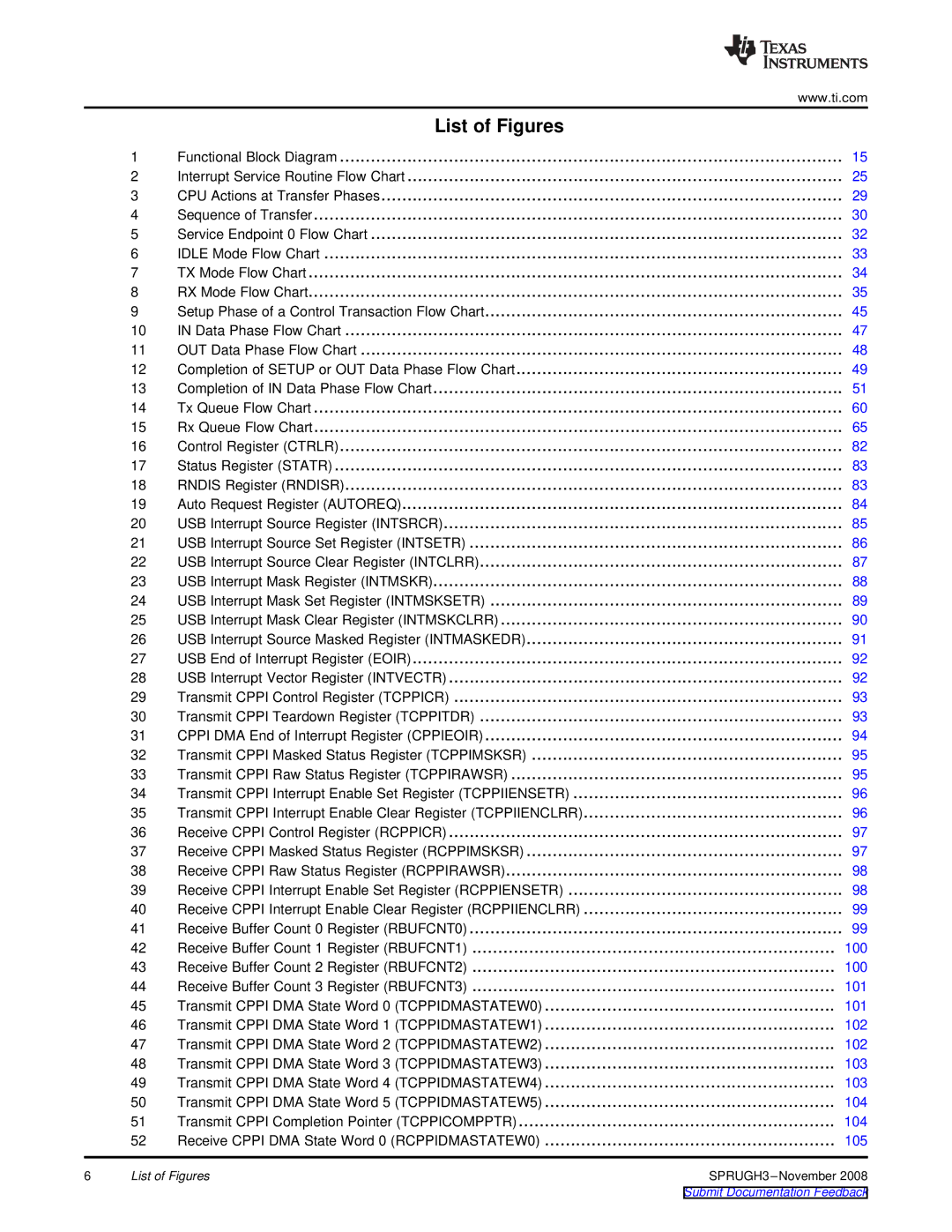

| List of Figures |

|

| 1 | Functional Block Diagram | 15 |

| 2 | Interrupt Service Routine Flow Chart | 25 |

| 3 | CPU Actions at Transfer Phases | 29 |

| 4 | Sequence of Transfer | 30 |

| 5 | Service Endpoint 0 Flow Chart | 32 |

| 6 | IDLE Mode Flow Chart | 33 |

| 7 | TX Mode Flow Chart | 34 |

| 8 | RX Mode Flow Chart | 35 |

| 9 | Setup Phase of a Control Transaction Flow Chart | 45 |

| 10 | IN Data Phase Flow Chart | 47 |

| 11 | OUT Data Phase Flow Chart | 48 |

| 12 | Completion of SETUP or OUT Data Phase Flow Chart | 49 |

| 13 | Completion of IN Data Phase Flow Chart | 51 |

| 14 | Tx Queue Flow Chart | 60 |

| 15 | Rx Queue Flow Chart | 65 |

| 16 | Control Register (CTRLR) | 82 |

| 17 | Status Register (STATR) | 83 |

| 18 | RNDIS Register (RNDISR) | 83 |

| 19 | Auto Request Register (AUTOREQ) | 84 |

| 20 | USB Interrupt Source Register (INTSRCR) | 85 |

| 21 | USB Interrupt Source Set Register (INTSETR) | 86 |

| 22 | USB Interrupt Source Clear Register (INTCLRR) | 87 |

| 23 | USB Interrupt Mask Register (INTMSKR) | 88 |

| 24 | USB Interrupt Mask Set Register (INTMSKSETR) | 89 |

| 25 | USB Interrupt Mask Clear Register (INTMSKCLRR) | 90 |

| 26 | USB Interrupt Source Masked Register (INTMASKEDR) | 91 |

| 27 | USB End of Interrupt Register (EOIR) | 92 |

| 28 | USB Interrupt Vector Register (INTVECTR) | 92 |

| 29 | Transmit CPPI Control Register (TCPPICR) | 93 |

| 30 | Transmit CPPI Teardown Register (TCPPITDR) | 93 |

| 31 | CPPI DMA End of Interrupt Register (CPPIEOIR) | 94 |

| 32 | Transmit CPPI Masked Status Register (TCPPIMSKSR) | 95 |

| 33 | Transmit CPPI Raw Status Register (TCPPIRAWSR) | 95 |

| 34 | Transmit CPPI Interrupt Enable Set Register (TCPPIIENSETR) | 96 |

| 35 | Transmit CPPI Interrupt Enable Clear Register (TCPPIIENCLRR) | 96 |

| 36 | Receive CPPI Control Register (RCPPICR) | 97 |

| 37 | Receive CPPI Masked Status Register (RCPPIMSKSR) | 97 |

| 38 | Receive CPPI Raw Status Register (RCPPIRAWSR) | 98 |

| 39 | Receive CPPI Interrupt Enable Set Register (RCPPIENSETR) | 98 |

| 40 | Receive CPPI Interrupt Enable Clear Register (RCPPIIENCLRR) | 99 |

| 41 | Receive Buffer Count 0 Register (RBUFCNT0) | 99 |

| 42 | Receive Buffer Count 1 Register (RBUFCNT1) | 100 |

| 43 | Receive Buffer Count 2 Register (RBUFCNT2) | 100 |

| 44 | Receive Buffer Count 3 Register (RBUFCNT3) | 101 |

| 45 | Transmit CPPI DMA State Word 0 (TCPPIDMASTATEW0) | 101 |

| 46 | Transmit CPPI DMA State Word 1 (TCPPIDMASTATEW1) | 102 |

| 47 | Transmit CPPI DMA State Word 2 (TCPPIDMASTATEW2) | 102 |

| 48 | Transmit CPPI DMA State Word 3 (TCPPIDMASTATEW3) | 103 |

| 49 | Transmit CPPI DMA State Word 4 (TCPPIDMASTATEW4) | 103 |

| 50 | Transmit CPPI DMA State Word 5 (TCPPIDMASTATEW5) | 104 |

| 51 | Transmit CPPI Completion Pointer (TCPPICOMPPTR) | 104 |

| 52 | Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0) | 105 |

6 | List of Figures | ||