www.ti.com | Registers |

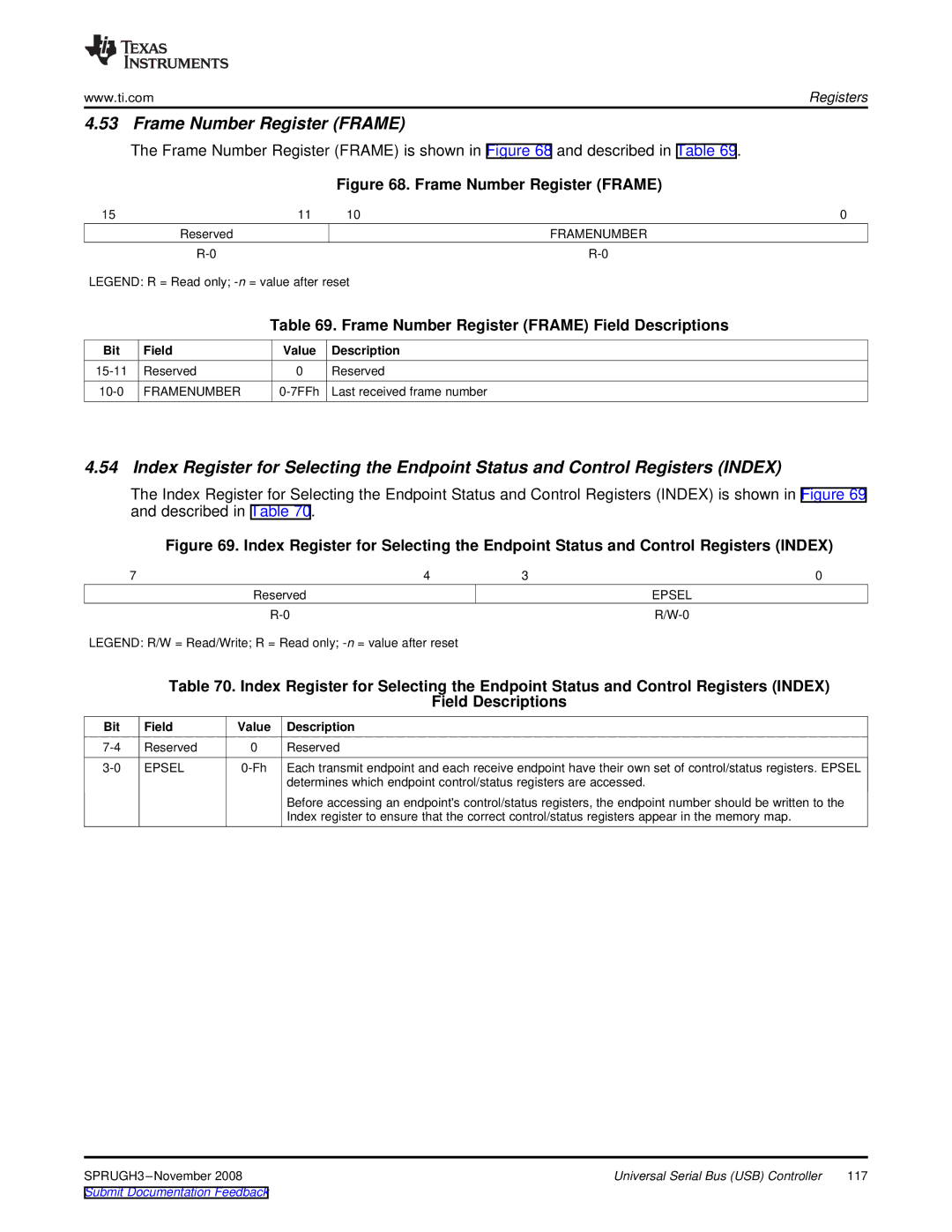

4.53 Frame Number Register (FRAME)

The Frame Number Register (FRAME) is shown in Figure 68 and described in Table 69.

Figure 68. Frame Number Register (FRAME)

15 | 11 | 10 | 0 |

| Reserved |

| FRAMENUMBER |

|

|

LEGEND: R = Read only;

Table 69. Frame Number Register (FRAME) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

FRAMENUMBER | Last received frame number |

4.54 Index Register for Selecting the Endpoint Status and Control Registers (INDEX)

The Index Register for Selecting the Endpoint Status and Control Registers (INDEX) is shown in Figure 69 and described in Table 70.

Figure 69. Index Register for Selecting the Endpoint Status and Control Registers (INDEX)

7 | 4 | 3 | 0 |

Reserved |

|

| EPSEL |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 70. Index Register for Selecting the Endpoint Status and Control Registers (INDEX)

Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

EPSEL | Each transmit endpoint and each receive endpoint have their own set of control/status registers. EPSEL | ||

|

|

| determines which endpoint control/status registers are accessed. |

Before accessing an endpoint's control/status registers, the endpoint number should be written to the

Index register to ensure that the correct control/status registers appear in the memory map.

Universal Serial Bus (USB) Controller | 117 | |

Submit Documentation Feedback |

|

|