USB Controller Host and Peripheral Modes Operation | www.ti.com |

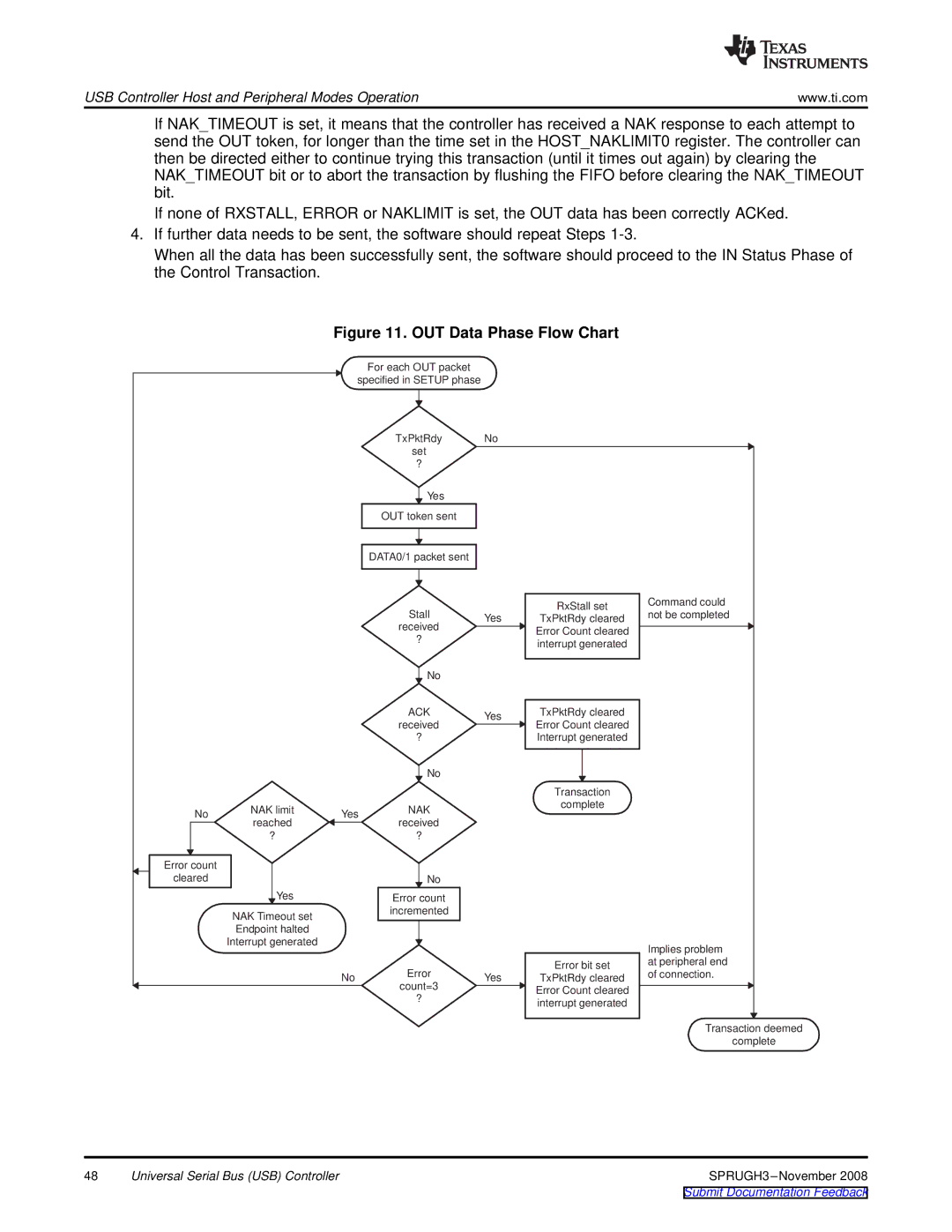

If NAK_TIMEOUT is set, it means that the controller has received a NAK response to each attempt to send the OUT token, for longer than the time set in the HOST_NAKLIMIT0 register. The controller can then be directed either to continue trying this transaction (until it times out again) by clearing the NAK_TIMEOUT bit or to abort the transaction by flushing the FIFO before clearing the NAK_TIMEOUT bit.

If none of RXSTALL, ERROR or NAKLIMIT is set, the OUT data has been correctly ACKed.

4.If further data needs to be sent, the software should repeat Steps

When all the data has been successfully sent, the software should proceed to the IN Status Phase of the Control Transaction.

Figure 11. OUT Data Phase Flow Chart

For each OUT packet

specified in SETUP phase

No | NAK limit | Yes | |

reached | |||

|

| ||

| ? |

|

Error count cleared

Yes

NAK Timeout set

Endpoint halted

Interrupt generated

No

48Universal Serial Bus (USB) Controller

TxPktRdy | No |

|

| |

set |

|

|

| |

? |

|

|

| |

Yes |

|

|

| |

OUT token sent |

|

|

| |

DATA0/1 packet sent |

|

|

| |

Stall |

| RxStall set | Command could | |

Yes | not be completed | |||

TxPktRdy cleared | ||||

received |

| |||

| Error Count cleared |

| ||

? |

|

| ||

| interrupt generated |

| ||

|

|

| ||

No |

|

|

| |

ACK | Yes | TxPktRdy cleared |

| |

received | Error Count cleared |

| ||

|

| |||

? |

| Interrupt generated |

| |

No |

|

|

| |

|

| Transaction |

| |

NAK |

| complete |

| |

|

|

| ||

received |

|

|

| |

? |

|

|

| |

No |

|

|

| |

Error count |

|

|

| |

incremented |

|

|

| |

|

|

| Implies problem | |

Error |

| Error bit set | at peripheral end | |

Yes | of connection. | |||

TxPktRdy cleared | ||||

count=3 |

| |||

| Error Count cleared |

| ||

? |

|

| ||

| interrupt generated |

| ||

|

|

| ||

|

|

| Transaction deemed | |

|

|

| complete | |

|

|

|