Registers | www.ti.com |

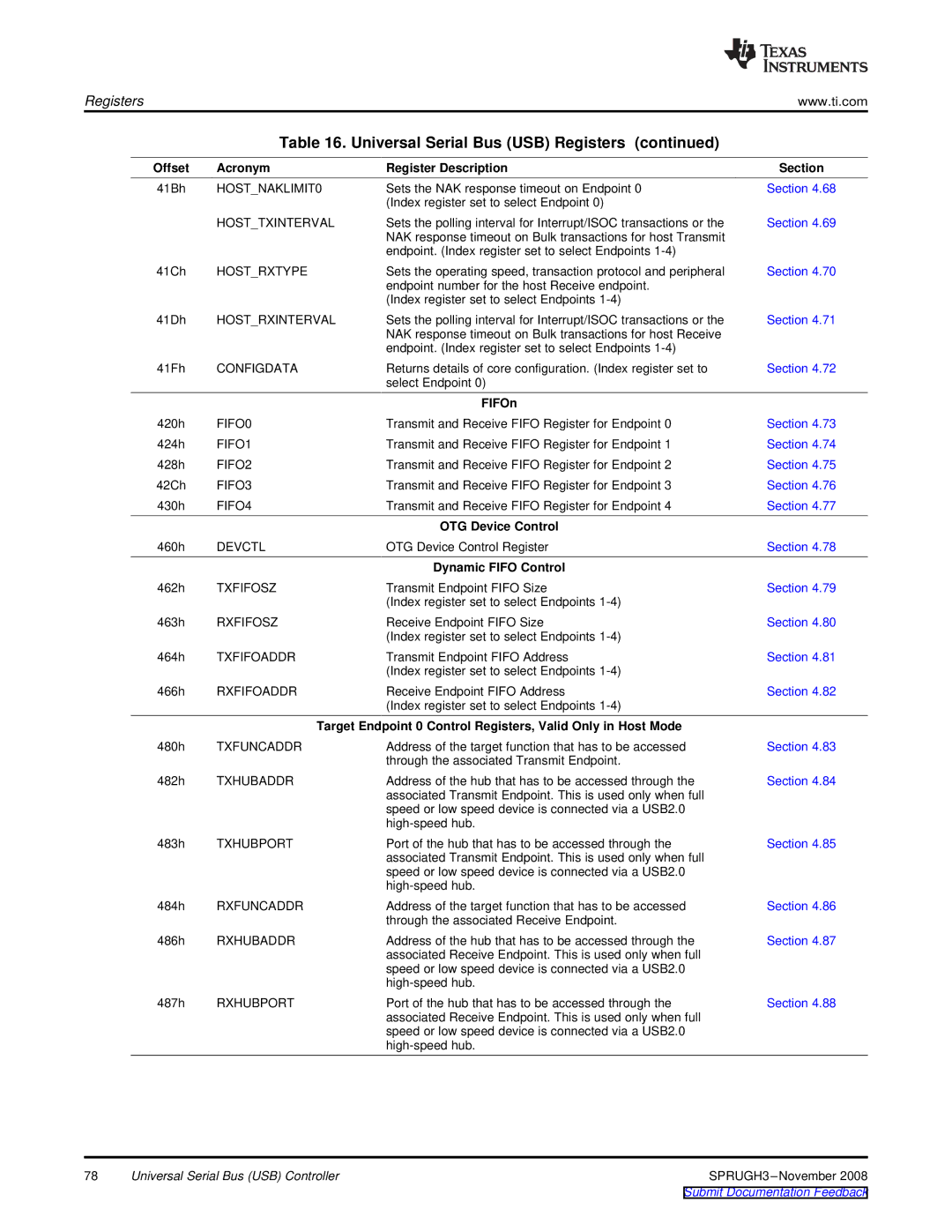

Table 16. Universal Serial Bus (USB) Registers (continued)

Offset | Acronym | Register Description | Section |

41Bh | HOST_NAKLIMIT0 | Sets the NAK response timeout on Endpoint 0 | Section 4.68 |

|

| (Index register set to select Endpoint 0) |

|

| HOST_TXINTERVAL | Sets the polling interval for Interrupt/ISOC transactions or the | Section 4.69 |

|

| NAK response timeout on Bulk transactions for host Transmit |

|

|

| endpoint. (Index register set to select Endpoints |

|

41Ch | HOST_RXTYPE | Sets the operating speed, transaction protocol and peripheral | Section 4.70 |

|

| endpoint number for the host Receive endpoint. |

|

|

| (Index register set to select Endpoints |

|

41Dh | HOST_RXINTERVAL | Sets the polling interval for Interrupt/ISOC transactions or the | Section 4.71 |

|

| NAK response timeout on Bulk transactions for host Receive |

|

|

| endpoint. (Index register set to select Endpoints |

|

41Fh | CONFIGDATA | Returns details of core configuration. (Index register set to | Section 4.72 |

|

| select Endpoint 0) |

|

|

| FIFOn |

|

420h | FIFO0 | Transmit and Receive FIFO Register for Endpoint 0 | Section 4.73 |

424h | FIFO1 | Transmit and Receive FIFO Register for Endpoint 1 | Section 4.74 |

428h | FIFO2 | Transmit and Receive FIFO Register for Endpoint 2 | Section 4.75 |

42Ch | FIFO3 | Transmit and Receive FIFO Register for Endpoint 3 | Section 4.76 |

430h | FIFO4 | Transmit and Receive FIFO Register for Endpoint 4 | Section 4.77 |

|

| OTG Device Control |

|

460h | DEVCTL | OTG Device Control Register | Section 4.78 |

|

| Dynamic FIFO Control |

|

462h | TXFIFOSZ | Transmit Endpoint FIFO Size | Section 4.79 |

|

| (Index register set to select Endpoints |

|

463h | RXFIFOSZ | Receive Endpoint FIFO Size | Section 4.80 |

|

| (Index register set to select Endpoints |

|

464h | TXFIFOADDR | Transmit Endpoint FIFO Address | Section 4.81 |

|

| (Index register set to select Endpoints |

|

466h | RXFIFOADDR | Receive Endpoint FIFO Address | Section 4.82 |

|

| (Index register set to select Endpoints |

|

| Target Endpoint 0 Control Registers, Valid Only in Host Mode |

| |

480h | TXFUNCADDR | Address of the target function that has to be accessed | Section 4.83 |

|

| through the associated Transmit Endpoint. |

|

482h | TXHUBADDR | Address of the hub that has to be accessed through the | Section 4.84 |

|

| associated Transmit Endpoint. This is used only when full |

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

| |

483h | TXHUBPORT | Port of the hub that has to be accessed through the | Section 4.85 |

|

| associated Transmit Endpoint. This is used only when full |

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

| |

484h | RXFUNCADDR | Address of the target function that has to be accessed | Section 4.86 |

|

| through the associated Receive Endpoint. |

|

486h | RXHUBADDR | Address of the hub that has to be accessed through the | Section 4.87 |

|

| associated Receive Endpoint. This is used only when full |

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

| |

487h | RXHUBPORT | Port of the hub that has to be accessed through the | Section 4.88 |

|

| associated Receive Endpoint. This is used only when full |

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

| |

78 | Universal Serial Bus (USB) Controller | |

|

| Submit Documentation Feedback |