Registerswww.ti.com

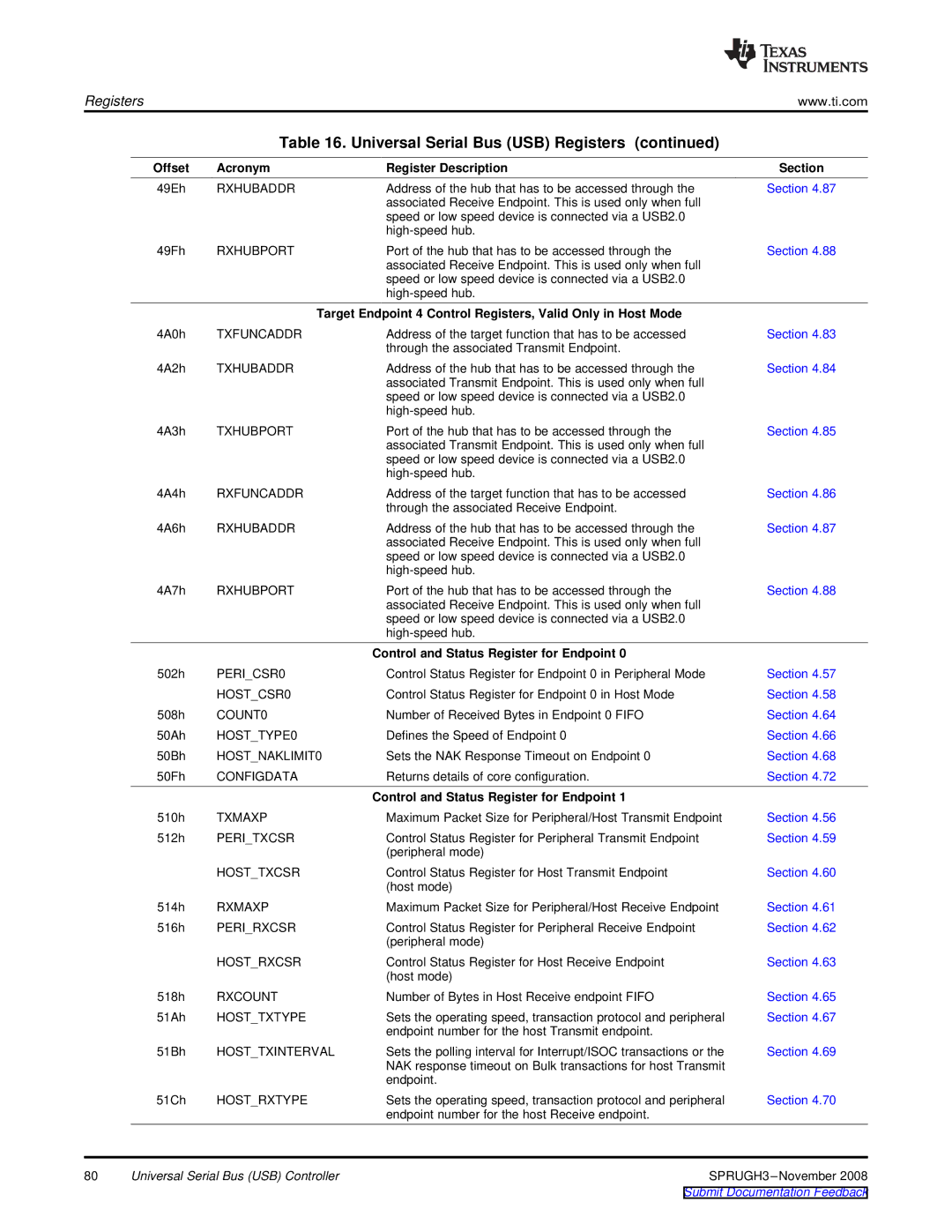

Table 16. Universal Serial Bus (USB) Registers (continued)

| Offset | Acronym | Register Description | Section |

| 49Eh | RXHUBADDR | Address of the hub that has to be accessed through the | Section 4.87 |

|

|

| associated Receive Endpoint. This is used only when full |

|

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

|

| |

| 49Fh | RXHUBPORT | Port of the hub that has to be accessed through the | Section 4.88 |

|

|

| associated Receive Endpoint. This is used only when full |

|

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

|

| |

|

| Target Endpoint 4 Control Registers, Valid Only in Host Mode |

| |

| 4A0h | TXFUNCADDR | Address of the target function that has to be accessed | Section 4.83 |

|

|

| through the associated Transmit Endpoint. |

|

| 4A2h | TXHUBADDR | Address of the hub that has to be accessed through the | Section 4.84 |

|

|

| associated Transmit Endpoint. This is used only when full |

|

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

|

| |

| 4A3h | TXHUBPORT | Port of the hub that has to be accessed through the | Section 4.85 |

|

|

| associated Transmit Endpoint. This is used only when full |

|

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

|

| |

| 4A4h | RXFUNCADDR | Address of the target function that has to be accessed | Section 4.86 |

|

|

| through the associated Receive Endpoint. |

|

| 4A6h | RXHUBADDR | Address of the hub that has to be accessed through the | Section 4.87 |

|

|

| associated Receive Endpoint. This is used only when full |

|

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

|

| |

| 4A7h | RXHUBPORT | Port of the hub that has to be accessed through the | Section 4.88 |

|

|

| associated Receive Endpoint. This is used only when full |

|

|

|

| speed or low speed device is connected via a USB2.0 |

|

|

|

|

| |

|

|

| Control and Status Register for Endpoint 0 |

|

| 502h | PERI_CSR0 | Control Status Register for Endpoint 0 in Peripheral Mode | Section 4.57 |

|

| HOST_CSR0 | Control Status Register for Endpoint 0 in Host Mode | Section 4.58 |

| 508h | COUNT0 | Number of Received Bytes in Endpoint 0 FIFO | Section 4.64 |

| 50Ah | HOST_TYPE0 | Defines the Speed of Endpoint 0 | Section 4.66 |

| 50Bh | HOST_NAKLIMIT0 | Sets the NAK Response Timeout on Endpoint 0 | Section 4.68 |

| 50Fh | CONFIGDATA | Returns details of core configuration. | Section 4.72 |

|

|

| Control and Status Register for Endpoint 1 |

|

| 510h | TXMAXP | Maximum Packet Size for Peripheral/Host Transmit Endpoint | Section 4.56 |

| 512h | PERI_TXCSR | Control Status Register for Peripheral Transmit Endpoint | Section 4.59 |

|

|

| (peripheral mode) |

|

|

| HOST_TXCSR | Control Status Register for Host Transmit Endpoint | Section 4.60 |

|

|

| (host mode) |

|

| 514h | RXMAXP | Maximum Packet Size for Peripheral/Host Receive Endpoint | Section 4.61 |

| 516h | PERI_RXCSR | Control Status Register for Peripheral Receive Endpoint | Section 4.62 |

|

|

| (peripheral mode) |

|

|

| HOST_RXCSR | Control Status Register for Host Receive Endpoint | Section 4.63 |

|

|

| (host mode) |

|

| 518h | RXCOUNT | Number of Bytes in Host Receive endpoint FIFO | Section 4.65 |

| 51Ah | HOST_TXTYPE | Sets the operating speed, transaction protocol and peripheral | Section 4.67 |

|

|

| endpoint number for the host Transmit endpoint. |

|

| 51Bh | HOST_TXINTERVAL | Sets the polling interval for Interrupt/ISOC transactions or the | Section 4.69 |

|

|

| NAK response timeout on Bulk transactions for host Transmit |

|

|

|

| endpoint. |

|

| 51Ch | HOST_RXTYPE | Sets the operating speed, transaction protocol and peripheral | Section 4.70 |

|

|

| endpoint number for the host Receive endpoint. |

|

80 | Universal Serial Bus (USB) Controller | |||