www.ti.com | Registers |

4.81 Transmit Endpoint FIFO Address (TXFIFOADDR)

Section 2.5 describes dynamically setting endpoint FIFO sizes.

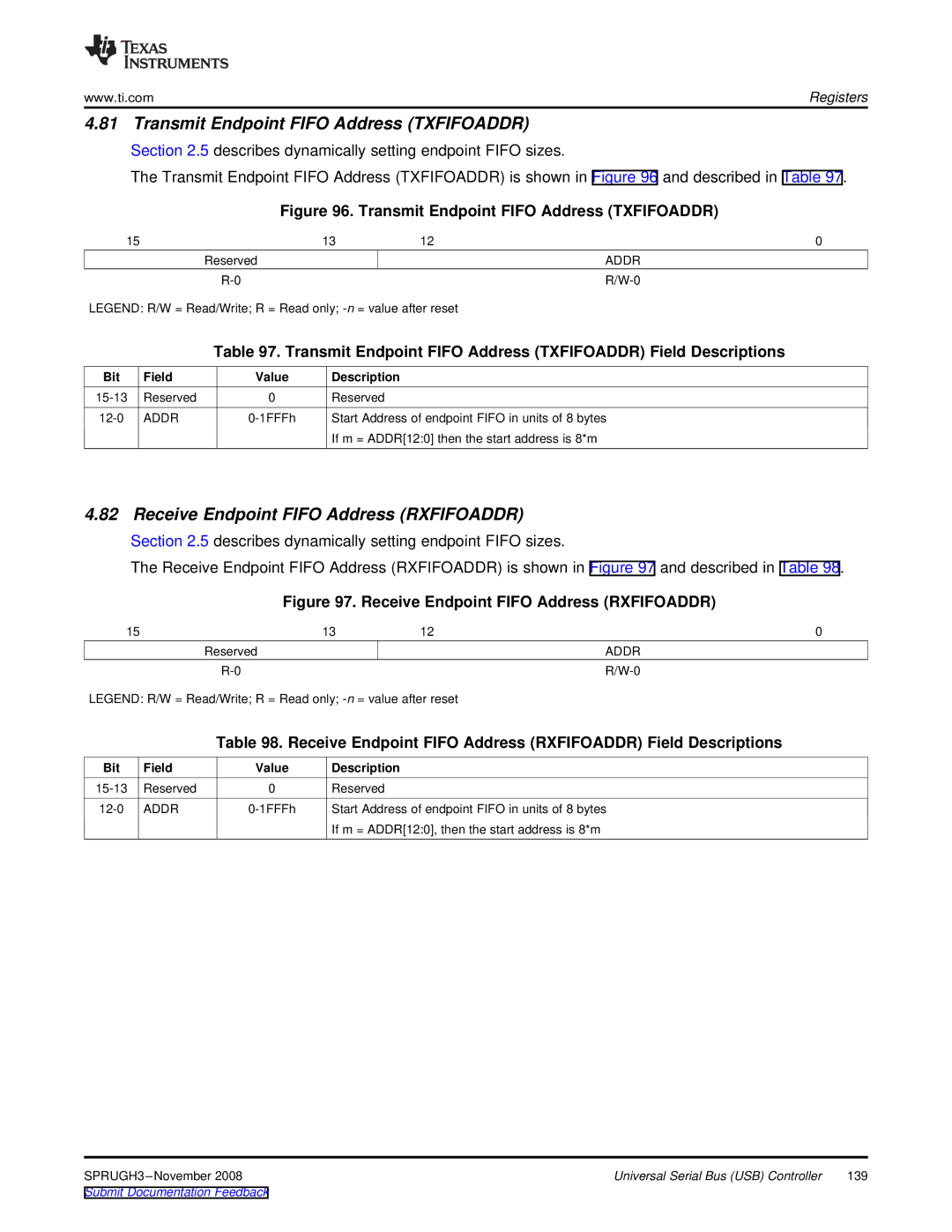

The Transmit Endpoint FIFO Address (TXFIFOADDR) is shown in Figure 96 and described in Table 97.

Figure 96. Transmit Endpoint FIFO Address (TXFIFOADDR)

15 | 13 | 12 | 0 |

| Reserved |

| ADDR |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 97. Transmit Endpoint FIFO Address (TXFIFOADDR) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

ADDR | Start Address of endpoint FIFO in units of 8 bytes | ||

|

|

| If m = ADDR[12:0] then the start address is 8*m |

4.82 Receive Endpoint FIFO Address (RXFIFOADDR)

Section 2.5 describes dynamically setting endpoint FIFO sizes.

The Receive Endpoint FIFO Address (RXFIFOADDR) is shown in Figure 97 and described in Table 98.

Figure 97. Receive Endpoint FIFO Address (RXFIFOADDR)

15 | 13 | 12 | 0 |

| Reserved |

| ADDR |

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 98. Receive Endpoint FIFO Address (RXFIFOADDR) Field Descriptions

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

ADDR | Start Address of endpoint FIFO in units of 8 bytes | ||

|

|

| If m = ADDR[12:0], then the start address is 8*m |

Universal Serial Bus (USB) Controller | 139 | |

Submit Documentation Feedback |

|

|