Registers | www.ti.com |

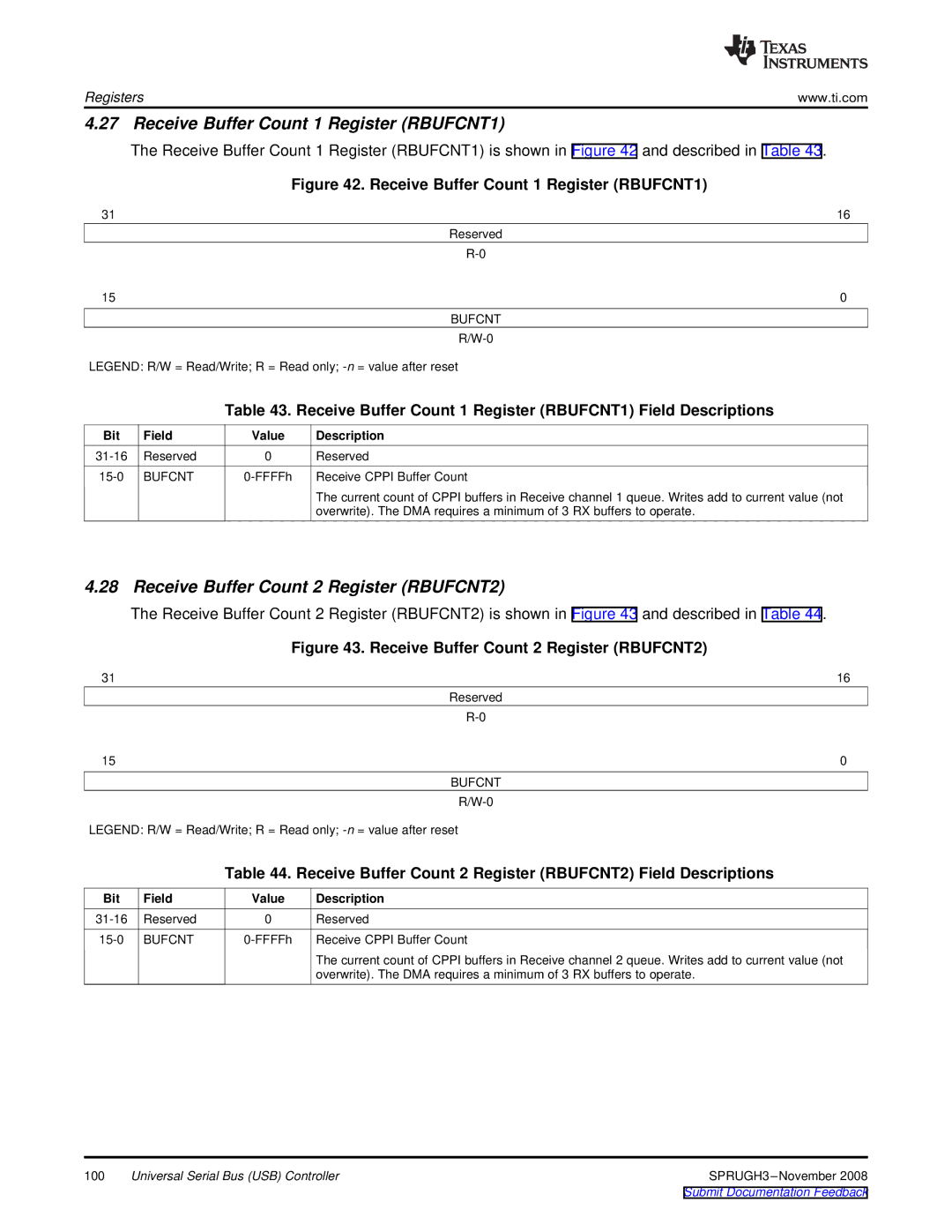

4.27 Receive Buffer Count 1 Register (RBUFCNT1)

The Receive Buffer Count 1 Register (RBUFCNT1) is shown in Figure 42 and described in Table 43.

|

| Figure 42. Receive Buffer Count 1 Register (RBUFCNT1) | |

31 |

|

| 16 |

|

|

| Reserved |

|

|

| |

15 |

|

| 0 |

|

|

| BUFCNT |

|

|

| |

LEGEND: R/W = Read/Write; R = Read only; | |||

|

| Table 43. Receive Buffer Count 1 Register (RBUFCNT1) Field Descriptions | |

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

BUFCNT | Receive CPPI Buffer Count | ||

|

|

| The current count of CPPI buffers in Receive channel 1 queue. Writes add to current value (not |

|

|

| overwrite). The DMA requires a minimum of 3 RX buffers to operate. |

4.28 Receive Buffer Count 2 Register (RBUFCNT2)

The Receive Buffer Count 2 Register (RBUFCNT2) is shown in Figure 43 and described in Table 44.

|

| Figure 43. Receive Buffer Count 2 Register (RBUFCNT2) | |

31 |

|

| 16 |

|

|

| Reserved |

|

|

| |

15 |

|

| 0 |

|

|

| BUFCNT |

|

|

| |

LEGEND: R/W = Read/Write; R = Read only; | |||

|

| Table 44. Receive Buffer Count 2 Register (RBUFCNT2) Field Descriptions | |

Bit | Field | Value | Description |

Reserved | 0 | Reserved | |

BUFCNT | Receive CPPI Buffer Count | ||

|

|

| The current count of CPPI buffers in Receive channel 2 queue. Writes add to current value (not |

|

|

| overwrite). The DMA requires a minimum of 3 RX buffers to operate. |

100 | Universal Serial Bus (USB) Controller |