www.ti.com |

|

|

|

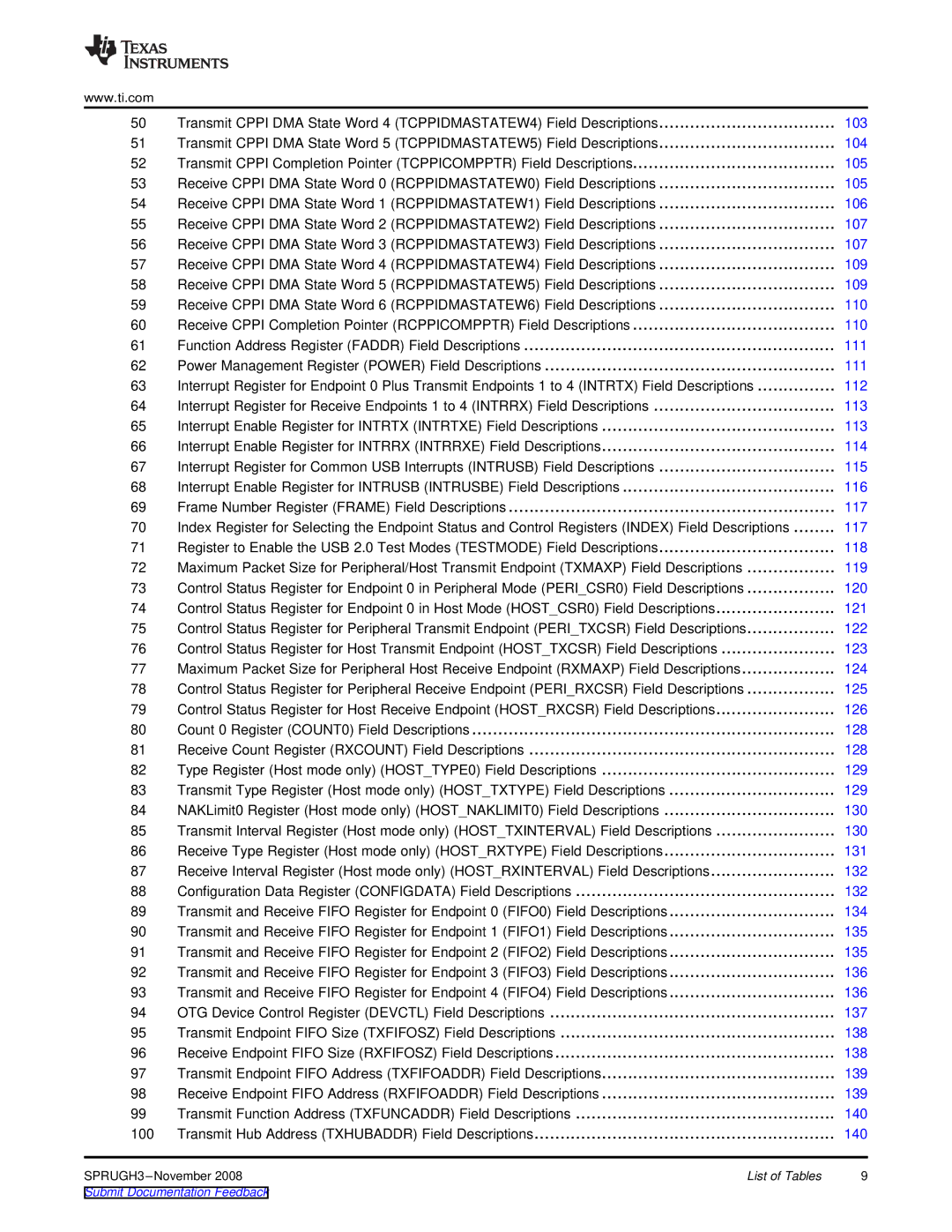

50 | Transmit CPPI DMA State Word 4 (TCPPIDMASTATEW4) Field Descriptions | 103 | |

51 | Transmit CPPI DMA State Word 5 (TCPPIDMASTATEW5) Field Descriptions | 104 | |

52 | Transmit CPPI Completion Pointer (TCPPICOMPPTR) Field Descriptions | 105 | |

53 | Receive CPPI DMA State Word 0 (RCPPIDMASTATEW0) Field Descriptions | 105 | |

54 | Receive CPPI DMA State Word 1 (RCPPIDMASTATEW1) Field Descriptions | 106 | |

55 | Receive CPPI DMA State Word 2 (RCPPIDMASTATEW2) Field Descriptions | 107 | |

56 | Receive CPPI DMA State Word 3 (RCPPIDMASTATEW3) Field Descriptions | 107 | |

57 | Receive CPPI DMA State Word 4 (RCPPIDMASTATEW4) Field Descriptions | 109 | |

58 | Receive CPPI DMA State Word 5 (RCPPIDMASTATEW5) Field Descriptions | 109 | |

59 | Receive CPPI DMA State Word 6 (RCPPIDMASTATEW6) Field Descriptions | 110 | |

60 | Receive CPPI Completion Pointer (RCPPICOMPPTR) Field Descriptions | 110 | |

61 | Function Address Register (FADDR) Field Descriptions | 111 | |

62 | Power Management Register (POWER) Field Descriptions | 111 | |

63 | Interrupt Register for Endpoint 0 Plus Transmit Endpoints 1 to 4 (INTRTX) Field Descriptions | 112 | |

64 | Interrupt Register for Receive Endpoints 1 to 4 (INTRRX) Field Descriptions | 113 | |

65 | Interrupt Enable Register for INTRTX (INTRTXE) Field Descriptions | 113 | |

66 | Interrupt Enable Register for INTRRX (INTRRXE) Field Descriptions | 114 | |

67 | Interrupt Register for Common USB Interrupts (INTRUSB) Field Descriptions | 115 | |

68 | Interrupt Enable Register for INTRUSB (INTRUSBE) Field Descriptions | 116 | |

69 | Frame Number Register (FRAME) Field Descriptions | 117 | |

70 | Index Register for Selecting the Endpoint Status and Control Registers (INDEX) Field Descriptions | 117 | |

71 | Register to Enable the USB 2.0 Test Modes (TESTMODE) Field Descriptions | 118 | |

72 | Maximum Packet Size for Peripheral/Host Transmit Endpoint (TXMAXP) Field Descriptions | ................. | 119 |

73 | Control Status Register for Endpoint 0 in Peripheral Mode (PERI_CSR0) Field Descriptions | ................. | 120 |

74 | Control Status Register for Endpoint 0 in Host Mode (HOST_CSR0) Field Descriptions | 121 | |

75 | Control Status Register for Peripheral Transmit Endpoint (PERI_TXCSR) Field Descriptions | 122 | |

76 | Control Status Register for Host Transmit Endpoint (HOST_TXCSR) Field Descriptions | 123 | |

77 | Maximum Packet Size for Peripheral Host Receive Endpoint (RXMAXP) Field Descriptions | 124 | |

78 | Control Status Register for Peripheral Receive Endpoint (PERI_RXCSR) Field Descriptions | ................. | 125 |

79 | Control Status Register for Host Receive Endpoint (HOST_RXCSR) Field Descriptions | 126 | |

80 | Count 0 Register (COUNT0) Field Descriptions | 128 | |

81 | Receive Count Register (RXCOUNT) Field Descriptions | 128 | |

82 | Type Register (Host mode only) (HOST_TYPE0) Field Descriptions | 129 | |

83 | Transmit Type Register (Host mode only) (HOST_TXTYPE) Field Descriptions | 129 | |

84 | NAKLimit0 Register (Host mode only) (HOST_NAKLIMIT0) Field Descriptions | 130 | |

85 | Transmit Interval Register (Host mode only) (HOST_TXINTERVAL) Field Descriptions | 130 | |

86 | Receive Type Register (Host mode only) (HOST_RXTYPE) Field Descriptions | 131 | |

87 | Receive Interval Register (Host mode only) (HOST_RXINTERVAL) Field Descriptions | 132 | |

88 | Configuration Data Register (CONFIGDATA) Field Descriptions | 132 | |

89 | Transmit and Receive FIFO Register for Endpoint 0 (FIFO0) Field Descriptions | 134 | |

90 | Transmit and Receive FIFO Register for Endpoint 1 (FIFO1) Field Descriptions | 135 | |

91 | Transmit and Receive FIFO Register for Endpoint 2 (FIFO2) Field Descriptions | 135 | |

92 | Transmit and Receive FIFO Register for Endpoint 3 (FIFO3) Field Descriptions | 136 | |

93 | Transmit and Receive FIFO Register for Endpoint 4 (FIFO4) Field Descriptions | 136 | |

94 | OTG Device Control Register (DEVCTL) Field Descriptions | 137 | |

95 | Transmit Endpoint FIFO Size (TXFIFOSZ) Field Descriptions | 138 | |

96 | Receive Endpoint FIFO Size (RXFIFOSZ) Field Descriptions | 138 | |

97 | Transmit Endpoint FIFO Address (TXFIFOADDR) Field Descriptions | 139 | |

98 | Receive Endpoint FIFO Address (RXFIFOADDR) Field Descriptions | 139 | |

99 | Transmit Function Address (TXFUNCADDR) Field Descriptions | 140 | |

100 | Transmit Hub Address (TXHUBADDR) Field Descriptions | 140 | |

List of Tables | 9 | ||