OR

LOGICAL OR | OR |

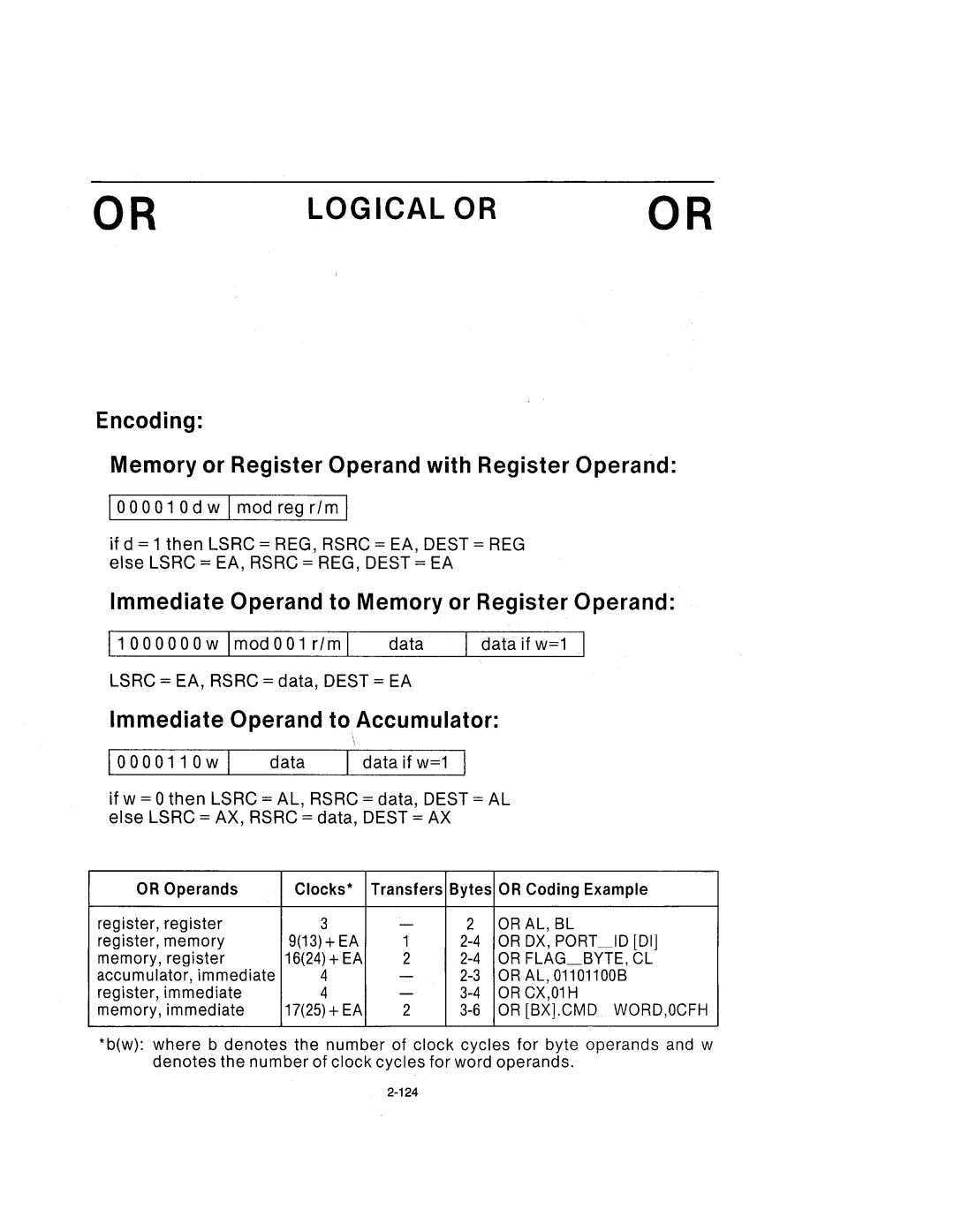

Encoding:

Memory or Register Operand with Register Operand:

100001 0 d w 1mod reg rIm 1

if d = 1 then LSRC = REG, RSRC = EA, DEST = REG else LSRC = EA, RSRC = REG, DEST = EA

Immediate Operand to Memory or Register Operand:

11 OOOOOOw Imod001 rIm 1 data· | data if w=1 |

LSRC = EA, RSRC = data, DEST = EA

Immediate Operand to Accumulator:

\

10 0 0 0 1 1 0 w 1 | data | 1 data if w=1 1 |

if w = 0 then LSRC = AL, RSRC = data, DEST = AL else LSRC = AX, RSRC = data, DEST = AX

OR Operands | Clocks* | Transfers Bytes OR Coding Example | ||

register, register | 3 | - | 2 | OR AL, BL |

register, memory | 9(13)+ EA | 1 | OR OX, PORT_10 [01] | |

memory, register | 16(24) + EA | 2 | OR FLAG_BYTE, CL | |

accumulator, immediate | 4 | - | OR AL, 01101100B | |

register, immediate | 4 | - | OR CX,01H | |

memory, immediate | 17(25)+ EA | 2 | OR [8X].CMO_WORO,OCFH | |

*b(w): where b denotes the number of clock cycles for byte operands and w denotes the number of clock cycles for word operands.