APPENDIX

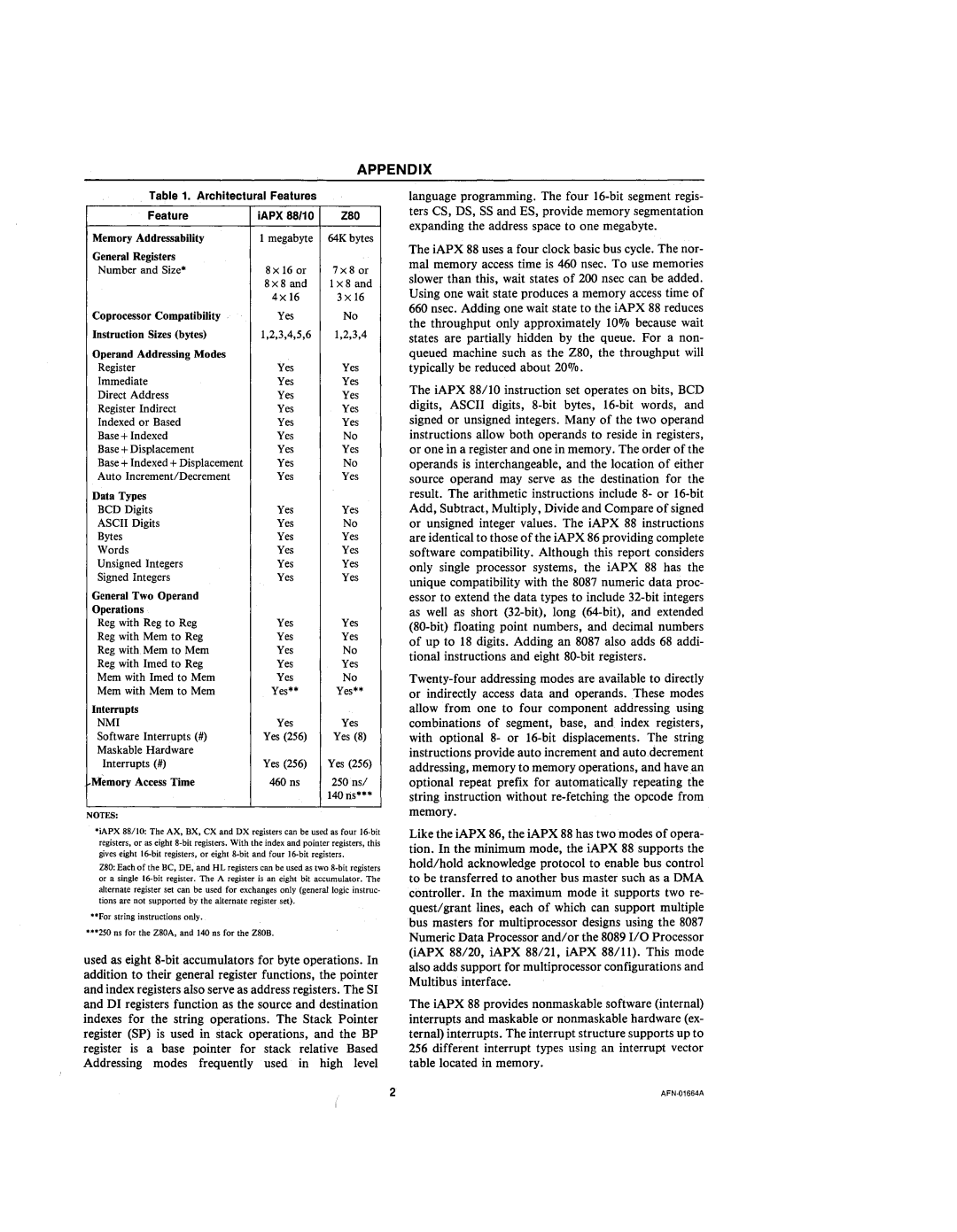

Table 1. Architectural Features |

| |

Feature | iAPX88/10 | Z80 |

Memory Addressability | 1 megabyte | 64K bytes |

General Registers |

|

|

Number and Size· | 8x 16 or | 7x8 or |

| 8x8 and | 1x8 and |

| 4xl6 | 3x 16 |

Coprocessor Compatibility " | Yes | No |

Instruction Sizes (bytes) | 1,2,3,4,5,6 | 1,2,3,4 |

Operand Addressing Modes |

|

|

Register | Yes | Yes |

Immediate | Yes | Yes |

Direct Address | Yes | Yes |

Register Indirect | Yes | Yes |

Indexed or Based | Yes | Yes |

Base + Indexed | Yes | No |

Base + Displacement | Yes | Yes |

Base + Indexed + Displacement | Yes | No |

Auto Increment/Decrement | Yes | Yes |

Data Types |

|

|

BCD Digits | Yes | Yes |

ASCII Digits | Yes | No |

Bytes | Yes | Yes |

Words | Yes | Yes |

Unsigned Integers | Yes | Yes |

Signed Integers | Yes | Yes |

General Two Operand |

|

|

Operations, |

|

|

Reg with Reg to Reg | Yes | Yes |

Reg with Mem to Reg | Yes | Yes |

Reg with Mem to Mem | Yes | No |

Reg with Imed to Reg | Yes | Yes |

Mem with Imed to Mem | Yes | No |

Mem with Mem to Mem | Yes·· | Yes·· |

Interrupts |

|

|

NMI | Yes | Yes |

Software Interrupts (#) | Yes (256) | Yes (8) |

Maskable Hardware | Yes (256) | Yes (256) |

Interrupts (#) | ||

Memory Access Time | 460 ns | 250ns/ |

|

| 140 lis··* |

NOTES:

*iAPX 88/10: The AX. BX. ex and DX registers can be used as four

registers, or as eight

gives eight

Z80: Each of the BC, DE; and HL registers can be used as two

or a single

**For string instructions only..

"·250 os for the Z80A, and 140 ns for the ZSOB.

used as eight

language programming. The four

The iAPX 88 uses a four clock basic bus cycle. The nor- mal memory access time is 460 nsec. To use memories slower than this, wait states of 200 nsec can be added. Using one wait state produces a memory access time of 660 nsec. Adding one wait state to the iAPX 88 reduces the throughput only approximately 10DJo because wait states are partially hidden by the queue. For a non- queued machine such as the Z80, the throughput will typically be reduced about 20DJo.

The iAPX 88/10 instruction set operates on bits, BCD digits, ASCII digits,

Like the iAPX 86, the iAPX 88 has two modes of opera- tion. In the minimum mode, the iAPX 88 supports the hold/hold acknowledge protocol to enable bus control to be transferred to another bus master such as a DMA controller. In the maximum mode it supports two re- quest/grant lines, each of which can support multiple bus masters for multiprocessor designs using the 8087 Numeric Data Processor and/or the 8089 I/O Processor (iAPX 88/20, iAPX 88/21, iAPX 88/11). This mode also adds support for multiprocessor configurations and Multibus interface.

The iAPX 88 provides nonmaskable software (internal) interrupts and maskable or nonmaskable hardware (ex- ternal) interrupts. The interrupt structure supports up to 256 different interrupt types using an interrupt vector table located in memory.

2 |