APPLICATION EXAMPLES

3)Reliability is improved by isolating sys- tem functions so a failure or error in one part of the system has a limited effect on the rest of the system.

4)Modular system design promotes parallel development of subsystems breaks the appli- cation into smaller, more manageable tasks, and helps isolate the effects of system modifications.

The iAPX 88 architecture supports two types of processors: independent processors and coprocessors.

An independent processor executes its own instruction stream. The 8088 CPU and 8089 I/O Processor are examples of independent processors. An 8088 typically executes a program in response to an interrupt. The lOP starts its channels in response to an interrupt- like signal called a channel attention; this signal is typically issued by a CPU.

The iAPX 88 product line architecture also supports processor extensions. The 8087 Numeric Processor Extension is an example. A special interface, designed into the 8088, allows this type of processor to be ac- comodated.

The processor extension adds additional registers, data types, and instruction re- sources directly to the system. When one 8087 is configured with one 8089 and an 8088, the system is referred to as iAPX88/21 (Fig.

iAPX 88 Multiprocessor Interface

The iAPX 88 architecture simplifies the development of

bus arbiters (system bus arbitration), or by a combination of the two, when processors have access to mUltiple shared busses. In all cases, the arbitration mechanism operates invisibly to software.

For mutual exclusion, each processor has a LOCK (bus lock) signal (program activated), to prevent other processors from obtaining a shared system bus.

The lOP may lock the bus during a DMA transfer to ensure both that the transfer completes in the shortest possible time, and that another processor does not access the target of the transfer (e.g., a buffer) while it is begin updated.

Each subsystem can examine and update a memory byte with the bus locked, using a LOCK prefix with the XCHG instruction. This instruction can be used to implement a semaphore mechanism for controlling the access of multiple processors to shared resources. A semaphore is a variable that indicates whether a resource, such as a buffer or a pointer, is "available" or "in use."

One multiprocessing system is shown in Figure

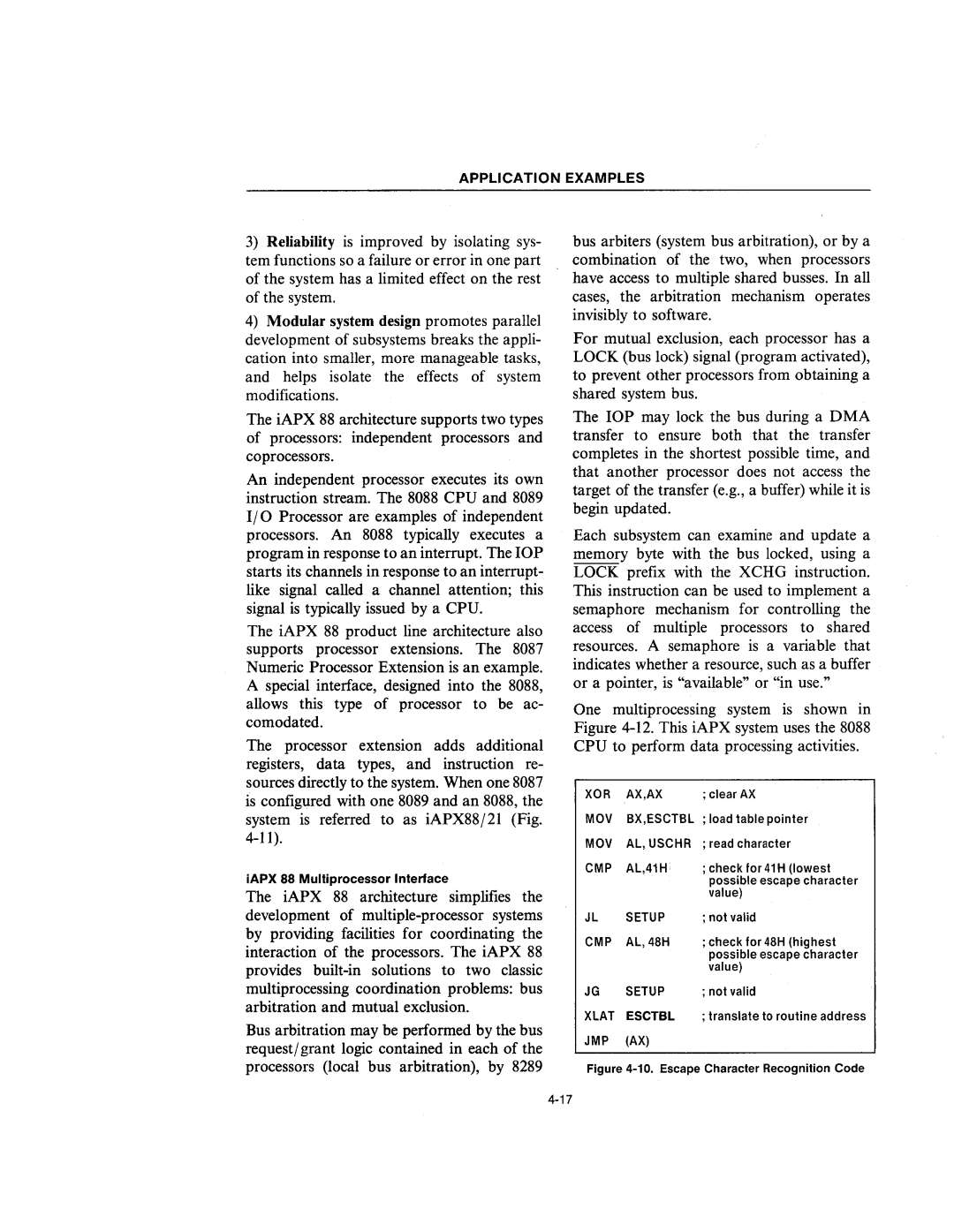

XOR | AX,AX | ; clear AX |

MOV | BX,ESCTBL | ; load table pointer |

MOV | AL, USCHR | ; read character |

CMP | AL,41H | ; check for41H (lowest |

|

| possible escape character |

|

| value) |

JL | SETUP | ; not valid |

CMP | AL,48H | ; check for 48H (highest |

|

| possible escape character |

|

| value) |

JG | SETUP | ; not valid |

XLAT | ESCTBL | ; translate to routine address |

Bus arbitration may be performed by the bus request/ grant logic contained in each of the processors (local bus arbitration), by 8289

JMP (AX)