iAPX 8.8110

"wait" states (Tw) are inserted between T3 and T4. Each inserted "wait" state is of the same duration as a ClK cycle. Periods can occur between 8088 driven bus cycles. These are referred to as "idle" states (Ti), or inactive ClK cycles. The processor uses these cycles for internal housekeeping.

During T1 of any bus cycle, the ALE (address latch enable) signal is emitted (by either the processor or the 8288 bus controller, depending on the MN/MX strap). At the trailing edge of this pulse, a valid address and certain status information for the cycle may be latched.

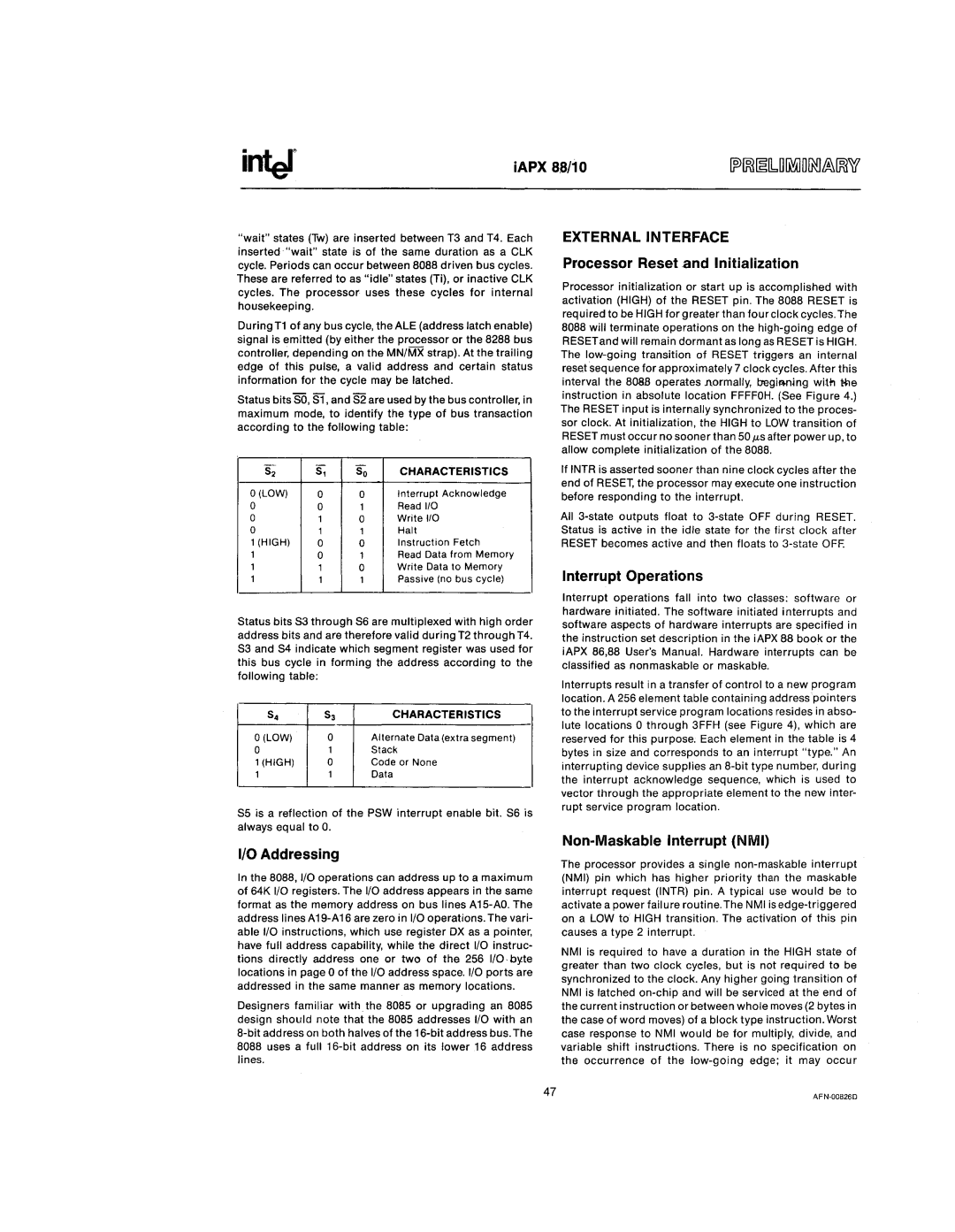

Status bits SO, 51, and S2 are used by the bus controller, in maximum mode, to identify the type of bus transaction according to the following table:

EXTERNAL INTERFACE

Processor Reset .and Initialization

Processor initialization or start up is accomplished with activation (HIGH) of the RESET pin. The 8088 RESET is required to be HIGH for greater than four clock cycles. The 8088 will terminate operations on the

- | - | - | CHARACTERISTICS |

52 | 51 | 50 | |

a (LOW) | 0 | 0 | Interrupt Acknowledge |

a | 0 | 1 | Read 110 |

0 | 1 | 0 | Write 1/0 |

a | 1 | 1 | Halt |

1 (HIGH) | a | 0 | Instruction Fetch |

1 | 0 | 1 | Read Data from Memory |

1 | 1 | a | Write Data to Memory |

1 | 1 | 1 | Passive (no bus cycle) |

Status bits S3 through S6 are multiplexed with high order address bits and are therefore valid during T2 through T4. S3 and S4 indicate which segment register was used for this bus cycle in forming the address according to the following table:

54 | 53 | CHARACTERISTICS |

a (LOW) | a | Alternate Data (extra segment) |

0 | 1 | Stack |

1 (HIGH) | 0 | Code or None |

1 | 1 | Data |

S5 is a reflection of the PSW interrupt enable bit. S6 is always equal to O.

If INTR is asserted sooner than nine clock cycles after the end of RESET, the processor may execute one instruction before responding to the interrupt.

All

Interrupt Operations

Interrupt operations fall into two classes: software or hardware initiated. The software initiated interrupts and software aspects of hardware interrupts are specified in the instruction set description in the iAPX 88 book or the iAPX 86,88 User'sManual. Hardware interrupts can be classified as nonmaskable or maskable.

Interrupts result in a transfer of control to a new program location. A 256 element table containing address pointers to the interrupt service program locations resides in abso- lute locations 0 through 3FFH (see Figure 4), which are reserved for this purpose. Each element in the table is 4 bytes in size and corresponds to an interrupt "type." An interrupting device supplies an

I/O Addressing

In the 8088, I/O operations can address up to a maximum of 64K I/O registers. The I/O address appears in the same format as the memory address on bus lines

Designers familiar with the 8085 or upgrading an 8085 design should note that the 8085 addresses I/O with an

Non-Maskable Interrupt (NMI)

The processor provides a single

NMI is required to have a duration in the HIGH state of greater than two clock cycles, but is not required to be synchronized to the clock. Any higher going transition of NMI is latched

47 |