INTRODUCTION

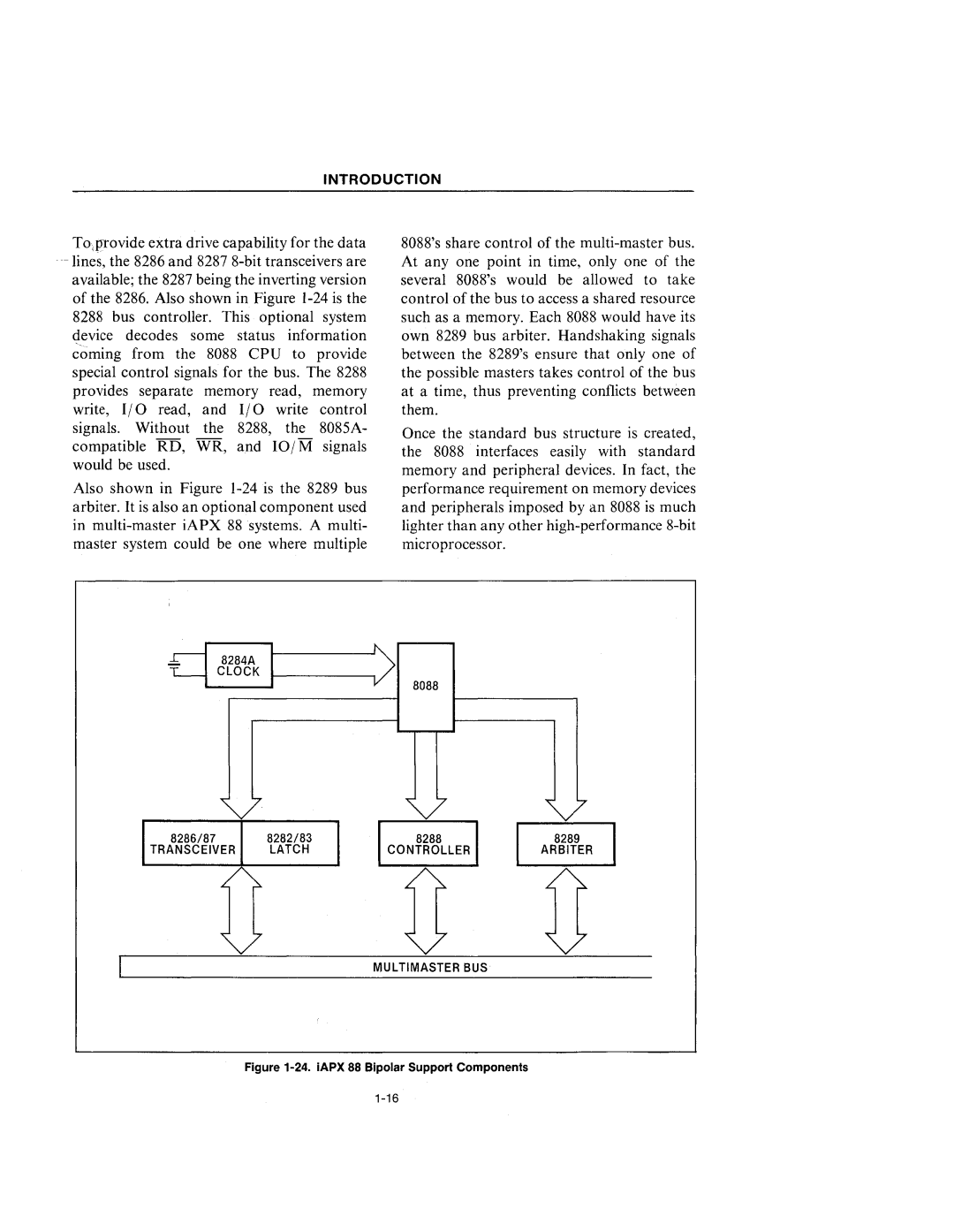

To,(ITovide extra drive capability for the data

device decodes some status information ~ming from the 8088 CPU to provide

special control signals for the bus. The 8288 provides separate memory read, memory write, 110 read, and 110 write control signals. Without the 8288, the 8085A- compatible RD, WR, and 101 M signals would be used.

Also shown in Figure

8088's share control of the

Once the standard bus structure is created, the 8088 interfaces easily with standard memory and peripheral devices. In fact, the performance requirement on memory devices and peripherals imposed by an 8088 is much lighter than any other

q 8284A I >

CLOCK

8088

~7 |

| V | V | I |

8286/87 | 8282/83 | 8288 | 8289 | |

TRANSCEIVER | LATCH | CONTROLLER | I ARBITER | |

/\,. |

| D D | ||

V |

| |||

MULTIMASTER BUS