8284A

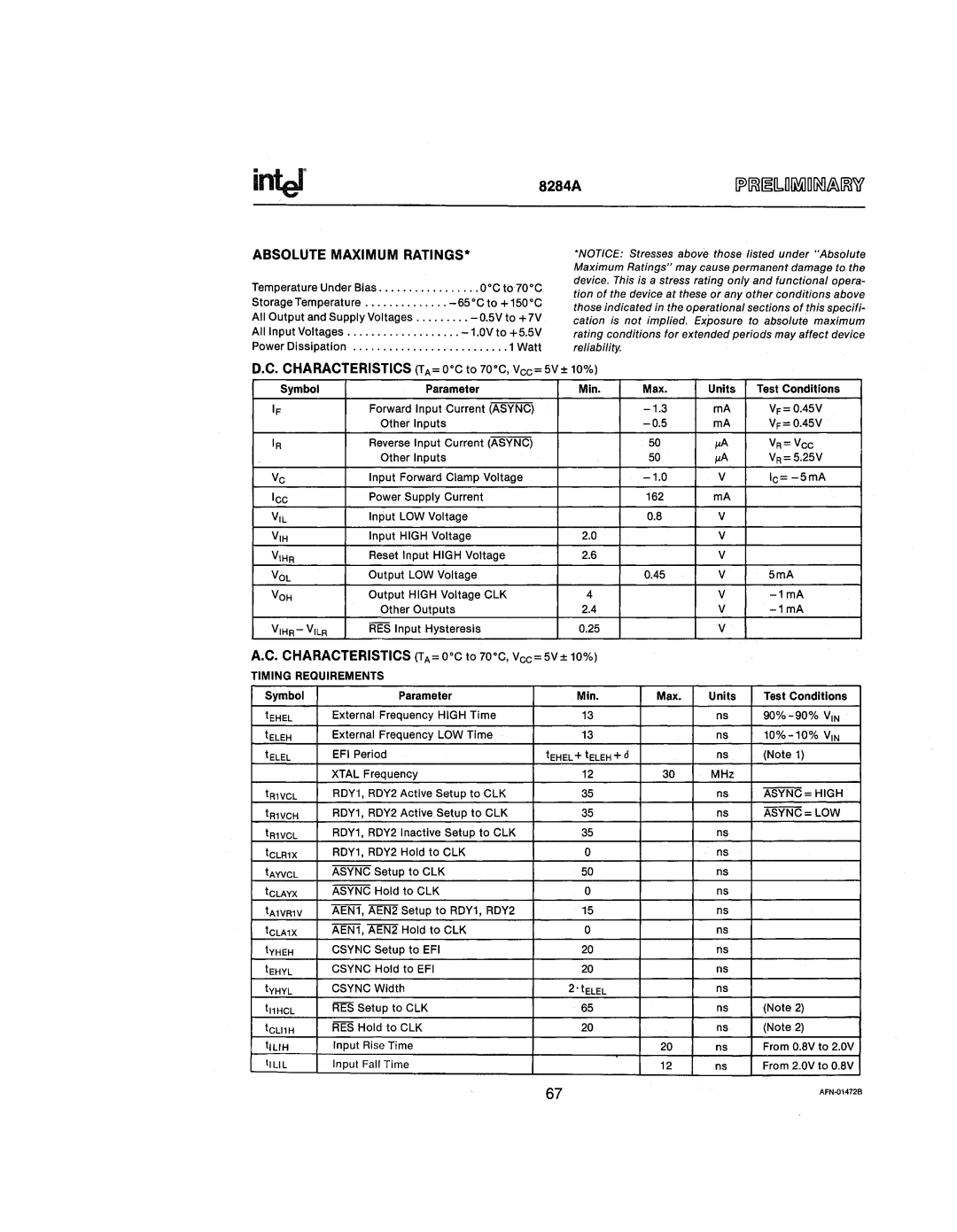

ABSOLUTE MAXIMUM RATINGS·

Temperature Under Bias | O·Cfo70·C |

Storage Temperature ..• | |

All Output and Supply Voltages | - 0.5V to + 7V |

All Input Voltages | |

Power Dissipation | 1 Watt |

'NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional opera- tion of the device at these or any other conditions above those indicated in the operational sections of ,this specifi- cation is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

D,C. CHARACTERISTICS (TA= O·Cto 70·C,Vcc= 5V± 10%) |

|

|

| ||

Symbol | Parameter | Min. | Max. | Units | Test Conditions |

IF | Forward Input Current (ASYNC) |

| mA | VF=0.45V | |

| Other Inputs |

| mA | VF= 0.45V | |

IA | Reverse Input Current (ASYNC) |

| 50 | ,.A | VR= Vcc |

| Other Inputs |

| 50 | ,.A | VR=5.25V |

Vc | input Forward Clamp Voltage |

| V | Ic= | |

Icc | Power Supply Current |

| 162 | mA |

|

VIL | Input lOW Voltage |

| 0.8 | V |

|

VIH | Input HIGH Voltage | 2.0 |

| V |

|

VIHA | Reset Input HIGH Voltage | 2.6 |

| V |

|

VOL | Output lOW Voltage |

| 0.45 | V | 5mA |

VOH | Output HIGH Voltage ClK | 4 |

| V | |

| Other Outputs | 2.4 |

| V | |

VIHA- VILA | RES Input Hysteresis | 0.25 |

| V |

|

A.C. CHARACTERISTICS (TA=O·Cto 70·C, Vcc=5V± 10%) |

|

|

| ||

TIMING REQUIREMENTS |

|

|

|

| |

Symbol | Parameter | Min. | Max. | Units | Test Conditions |

tEHEL | External Frequency HIGH Time | 13 |

| ns | |

tELEH | External Frequency lOW Time | 13 |

| ns | |

tELEL | EFI Period | tEHEL + tELEH + d |

| ns | (Note 1) |

| XTAl Frequency | 12 | 30 | MHz |

|

tA1VCL | RDY1, RDY2 Active Setup to ClK | 35 |

| ns | ASYNC=HIGH |

tR1VCH | RDY1, RDY2 Active Setup to ClK | 35 |

| ns | ASYNC=lOW |

tR1VCL | RDY1, RDY2 Inactive Setup to ClK | 35 |

| ns |

|

tCLA1X | RDY1, RDY2 Hold to ClK | 0 |

| ns |

|

tAYVCL | ASYNC Setup to ClK | 50 |

| ns |

|

tCLAYX | ASYNC Hold to ClK | 0 |

| ns |

|

tA1VA1V | AEN1, AEN2 Setup to RDY1, RDY2 | 15 |

| ns |

|

tCLA1X | AEN1, AEN2 Hold to ClK | 0 |

| ns |

|

tYHEH | CSYNC Setup to EFI | 20 |

| ns |

|

tEHYL | CSYNC Hold to EFI | 20 |

| ns |

|

tYHYL | CSYNCWidth | 2·tELEL |

| ns |

|

tllHCL | RES Setup to ClK | 65 |

| ns | (Note 2) |

tCLllH | RES Hold to ClK | 20 |

| ns | (Note 2) |

IIUH | Input Rise Time |

| 20 | ns | From O.SV 10 2.0V |

II LlL | Input Fall Time |

| 12 | ns | From 2.0V to O.SV |

67 | AFN.Q1472B |

|