!

<0

"T1

!C'

c:

iil

...f'

!'>

~

"C

(:;'

e!.

l>

"C

x

ex>

ex>

r-

0 n

e!.

:s::

0

(j)

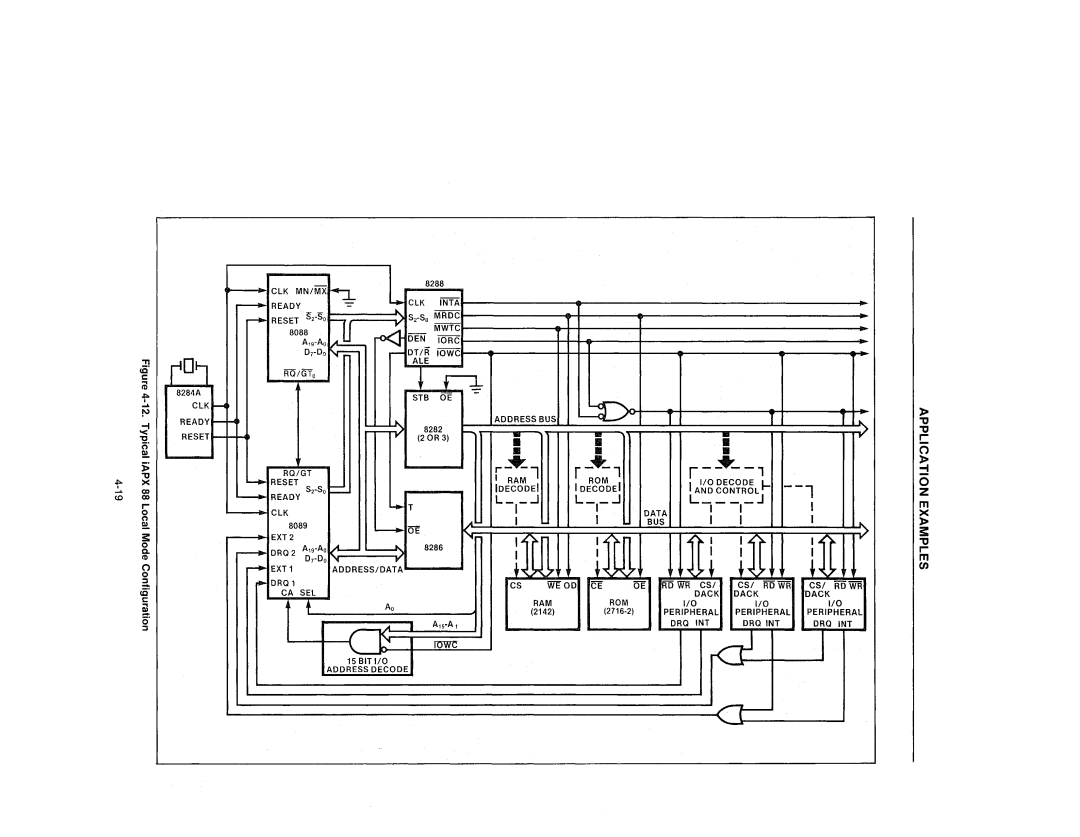

8284A

ClK

READY f -

RESET f -

r

......

.-

ClK MN/MX h

READY

RESET 5"So

8088A19- AO [JL

D"Do r--r-n

RO/GTo

RO/GT

RESET

S,'So~

READY

ClK

8089

EXT 2

DRO 2 A".A

D,'Do ...

L 8288

.. ClK INTA

r<l S,'So MRDC MWTC DEN_ 10RC

r - DT/R 10WC

ALE

+~

STB OE

j..

"V 8282

J. 8286

~

ADDRESS BUS

i

II

r"*l

IRAM

IDECODEI

L- I

J~ ~I~

L:D | 1 |

| T.. |

|

| 1 |

i.. |

|

|

|

|

| |

|

| |||||

1D:c?~DEI |

| 1AI~g g6~~~6l ~ |

| |||

L_1_.J |

| L ____ J | 1 |

| ||

| 1 | 1 |

|

| ||

| DATA |

| .. | |||

1 | 1 | 1 |

| 1 | ||

BUS |

| |||||

|

| |||||

I'"}. |

| ... ).1 | I~ | ~ |

| ). i" |

| 1 | 1 | I'" | |||

I |

|

| l~ |

| ||

|

|

|

|

|

| |

:x>

"t]

"t]

c

(")

:x>

::!

o z

m x :x> :s::

"t]

r- m

CJ)

(")

0

EXT 1 ADDRESS/DATA

1... 7 | '... 7~ h 7 | 7 |

a

!c'

c:

~

0'

::I

, . DRO 1 |

|

| CS | WEOD | CE | OE | RD WR | CSt | CSt RD WR | CSt | RD WR' |

CA SEl |

|

|

|

|

|

|

| DACK | DACK | DACK |

|

• | Ao |

|

| RAM |

| ROM | I/O | I/O | I/O | ||

|

| (2142) |

| (2716,2) | PERIPHERAL | PERIPHERAL | PERIPHERAL | ||||

|

|

|

| ||||||||

|

| A15'A |

|

|

| DRO | INT | DRO INT | DRO | INT | |

" | '"II | I | mwc |

|

|

|

| d |

|

| |

\ | l |

|

|

|

|

|

|

| |||

ADDRESS1~ODECODE,I |

|

|

|

|

|

|

| ||||

cr-