inter

Pin

8282/8283

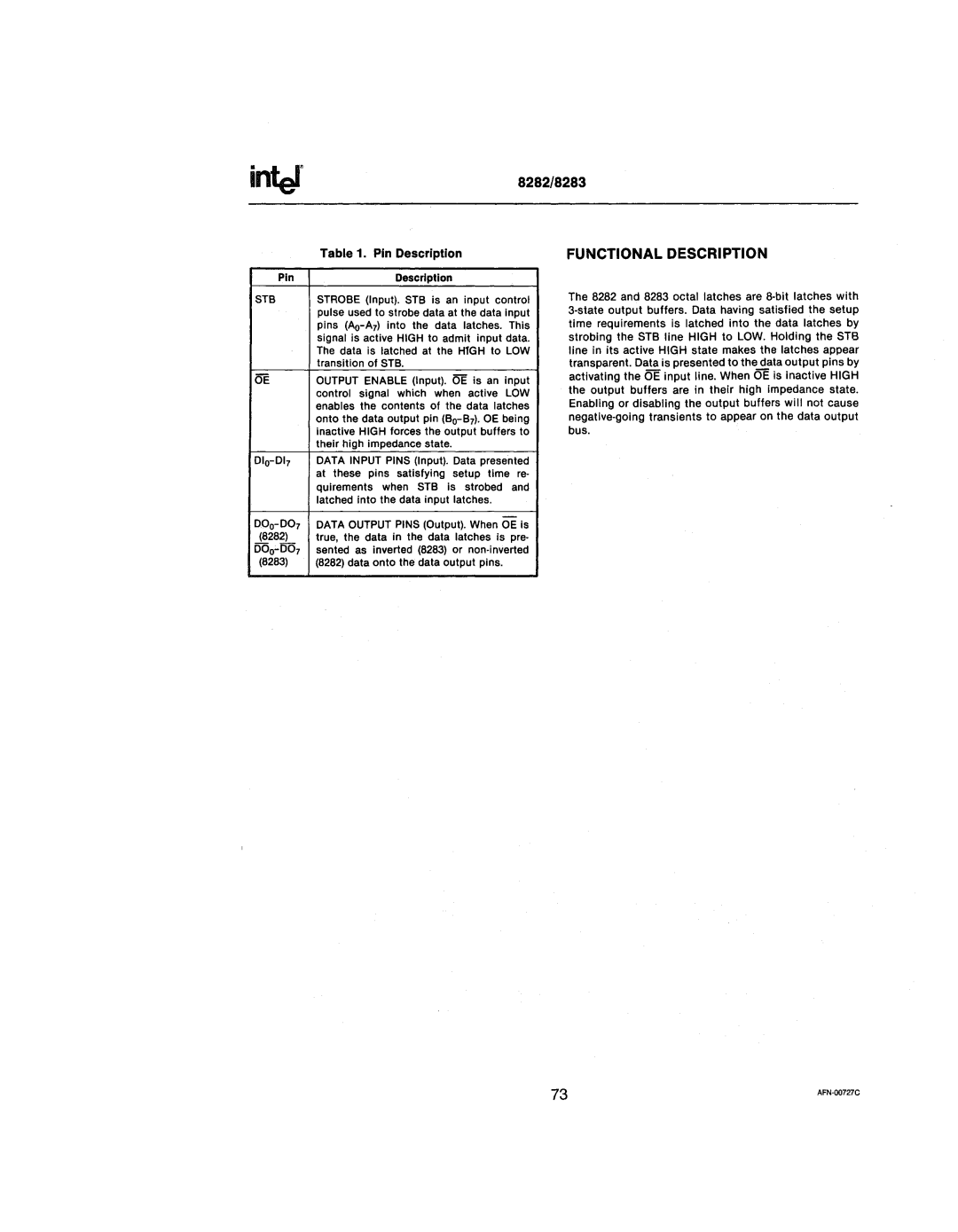

Table 1. Pin Description | FUNCTIONAL DESCRIPTION |

Description

STB

OE

STROBE (Input). STB is an input control pulse used to strobe data at the data input pins

OUTPUT ENABLE (Input). i5E is an input control signal which when active LOW enables the contents of the data latches onto the data output pin

DATA INPUT PINS (Input). Data presented at these pins satisfying setup time re- quirements when STB Is strobed and latched into the data input latches.

The 8282 and 8283 octal latches are 8·bit latches with

090- 007

(8282)

000:..007

(8283)

DATA OUTPUT PINS (Output). When OE Is true, the data in the data latches is pre· sented as Inverted (8283) or non·inverted (8282) data onto the data output pins.

73 | |

|