REF REFERENCES REF

FOR INSTRUCTION SET

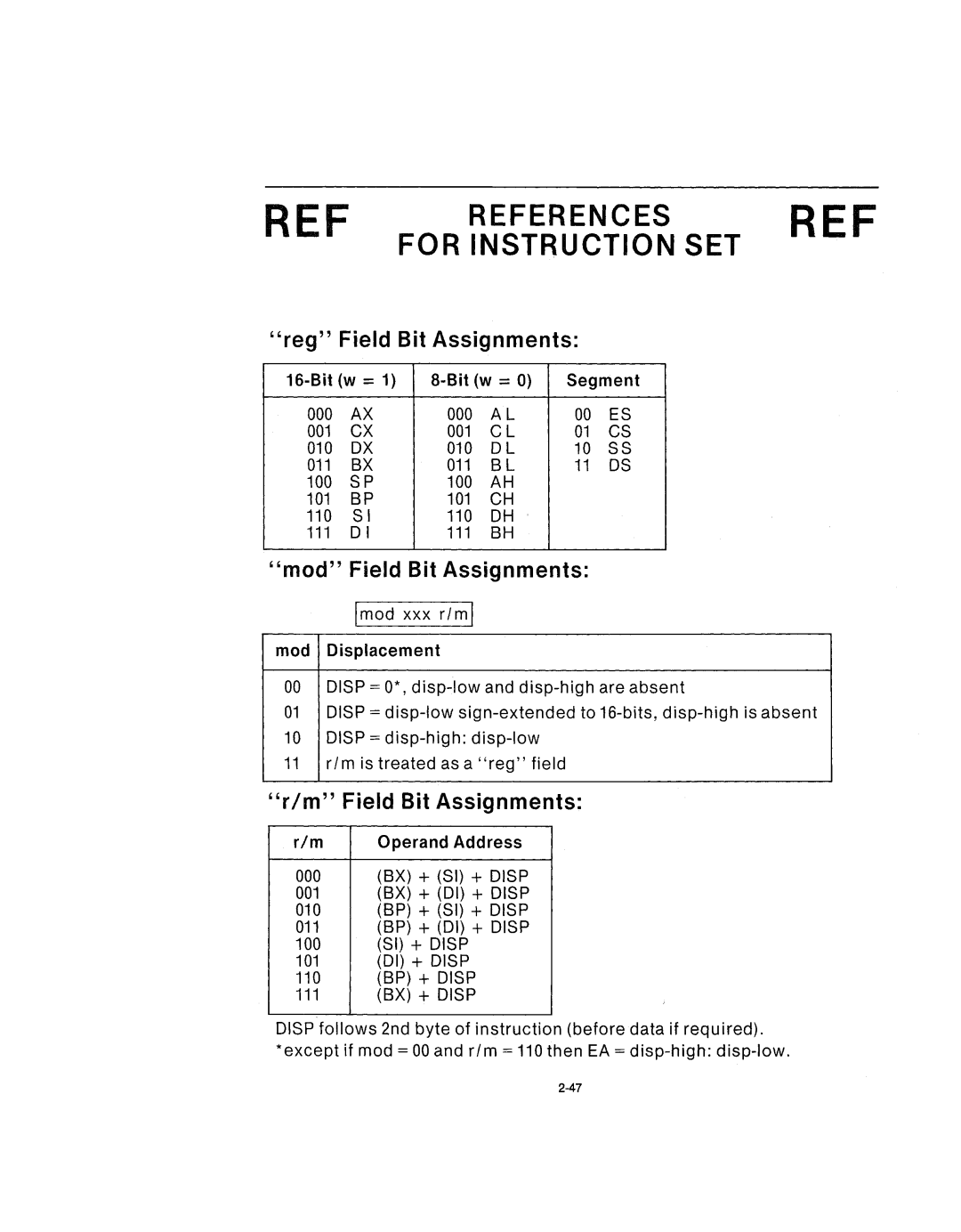

"reg" Field Bit Assignments:

Segment | |||||

000 | AX | 000 | AL | 00 | ES |

001 | CX | 001 | CL | 01 | CS |

010 | OX | 010 | OL | 10 | SS |

011 | BX | 011 | BL | 11 | OS |

100 | SP | 100 | AH |

|

|

101 | BP | 101 | CH |

|

|

110 | SI | 110 | OH |

|

|

111 | 01 | 111 | BH |

|

|

"mod" Field Bit Assignments:

Imod xxx r/ml

mod Displacement

00 OISP = 0*,

01OISP =

10OISP =

11rIm is treated as a "reg" field

"r1m" Field Bit Assignments:

rim Operand Address

000(BX) + (SI) + OISP

001(BX) + (01) + OISP

010(BP) + (SI) + OISP

011(BP) + (01) + OISP

100(SI) + OISP

101(01) + OISP

110(BP) + OISP

111(BX) + OISP

OISP follows 2nd byte of instruction (before data if required). *except if mod = 00 and rIm = 110 then EA =