SAR SHIFT ARITHMETIC SAR

RIGHT

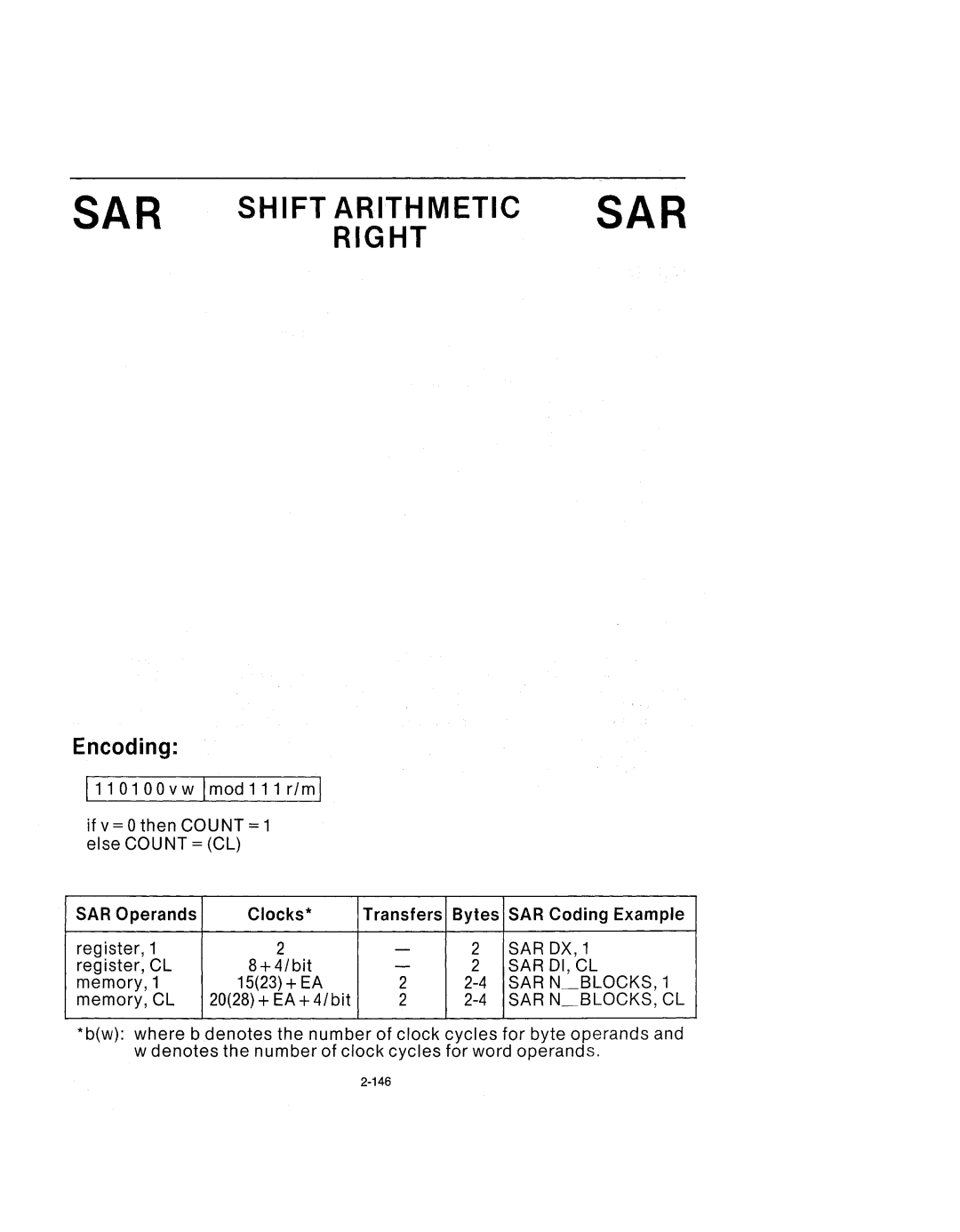

Encoding:

111 01 00 v w 1mod 111 rim I

ifv=OthenCOUNT=1 else COU NT = (CL)

SAR Operands | Clocks* | Transfers | Bytes SAR Coding Example | |

register, 1 | 2 | - | 2 | SAR OX, 1 |

register, CL | 8+ 4/bit | - | 2 | SAR 01, CL |

memory, 1 | 15(23) + EA | 2 | SAR N~BLOCKS, 1 | |

memory, CL | 20(28) + EA + 41 bit | 2 | SAR N~BLOCKS, CL | |

*b(w): where b denotes the number of clock cycles for byte operands and w denotes the number of clock cycles for word operands.