HARDWARE DESIGN

EXTERNAL INTERRUPTS

The 8088 has two inputs that may be used by external devices to signal interrupts, INTR and NMI.

The INTR (Interrupt Request) line is usually driven by an Intel® 8259A Programmable Interrupt Controller (PIC), which is in turn connected to the devices that need interrupt service. The 8259A is a very flexible compo- nent that is controlled by software com- mands from the iAPX 88. The PIC appears as a set of I/O ports to the software.

The 8259A's main job is to accept interrupt requests from the devices attached to it, determine which requesting device has high- est priority, then activate the iAPX 88 INTR line if the selected device has higher priority than the device currently being serviced (if any).

When INTR is active, the CPU takes different action depending on the state of the interrupt- enable flag (IF). No action takes place, however, until the currently executing instruc- tion has been completed. Some unusual cases are described under the heading of Interrupt Latency Exceptions. Then, if IF is clear - meaning that interrupts signaled on INTR are masked or disabled - the CPU ignores the interrupt request and processes the next instruction.

The INTR signal is not latched by the CPU, so it must be held active until a response is received or the request is withdrawn.

If interrupts on INTR are enabled (if IF is "1"), the CPU recognizes the interrupt request and processes it. Interrupt requests arriving on INTR can be enabled by executing an STI (set

Note that to reduce the likelihood of exces- sive stack

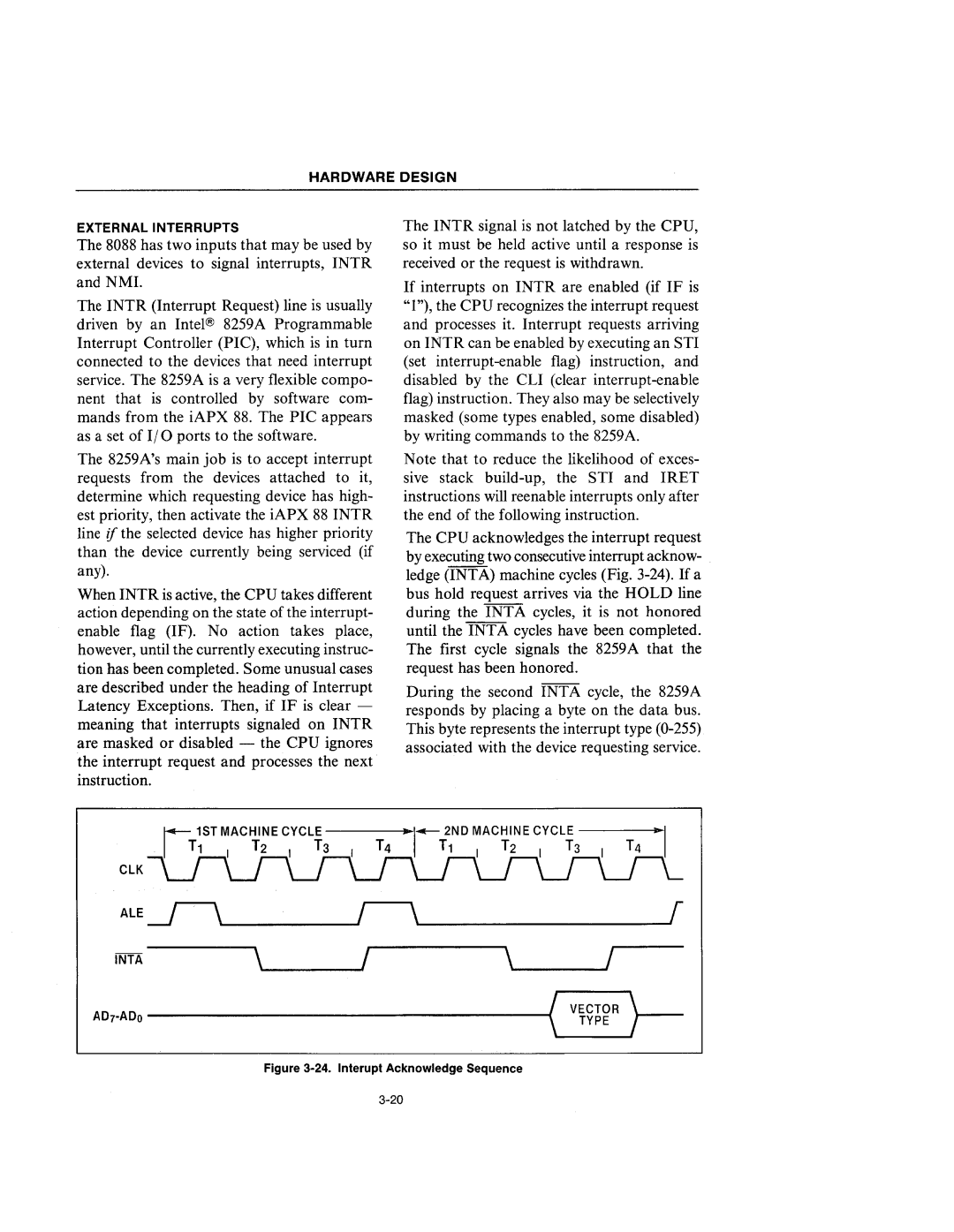

The CPU acknowledges the interrupt request by executing two consecutive interrupt acknow- ledge (INTA) machine cycles (Fig.

During the second INTA cycle, the 8259A responds by placing a byte on the data bus. This byte represents the interrupt type

| _1_ 2ND MACHINE CYCLE |

| |

T4 | T1 I T2 I | T3 |

|

ClK |

|

|

|

I | \ |

| r |

\ | I | ) | |

| ( | VECTOR | |

~ | TYPE |

| |