inter

iAPX 88/10

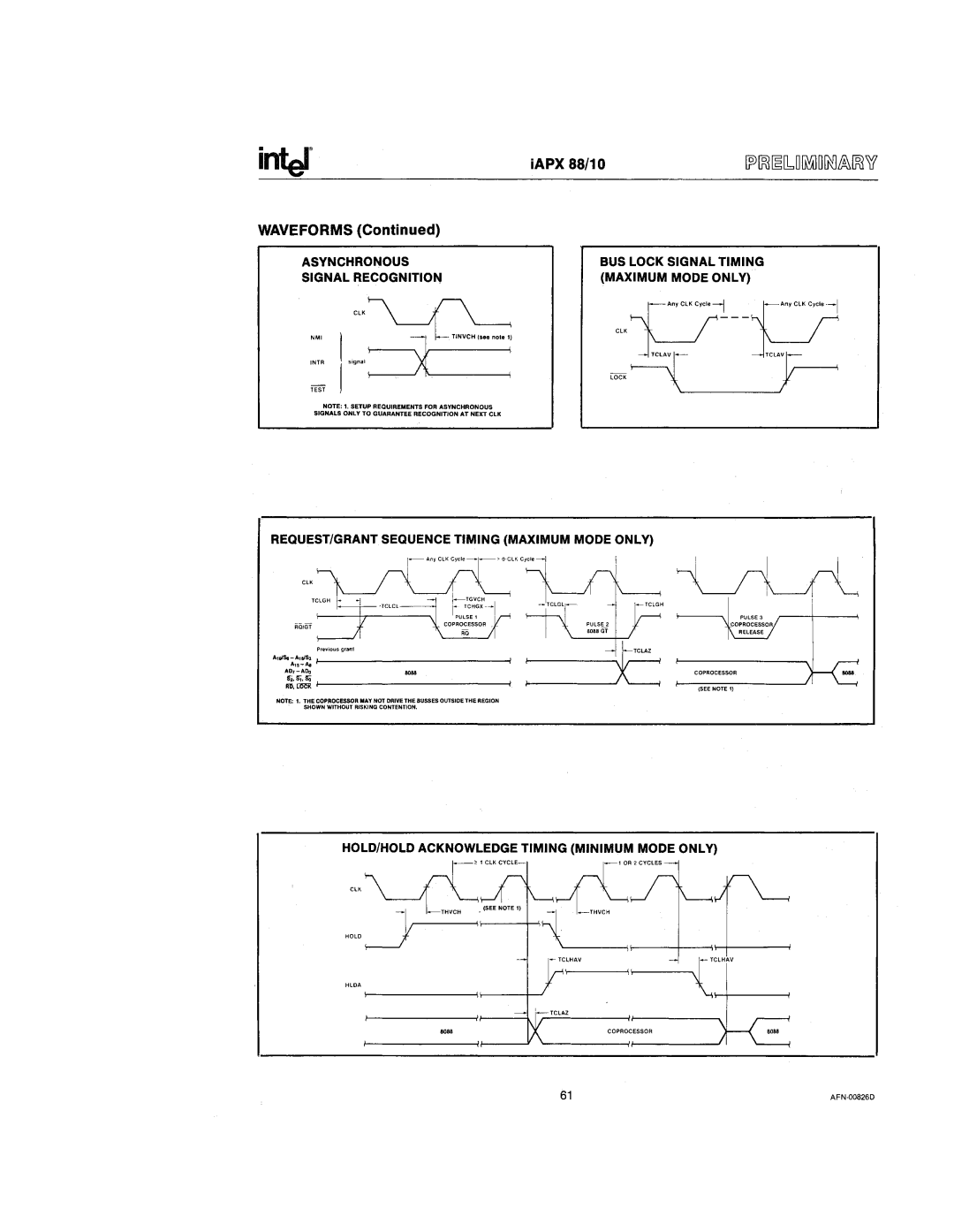

WAVEFORMS (Continued)

ASYNCHRONOUS |

| BUS LOCK SIGNAL TIMING |

|

SIGNAL RECOGNITIO",! | (MAXIMUM MODE ONLy) |

| |

ClK\ | Any eLK | Any eLK Cycle | |

NMI

INTR

I 1L.~~

I"gO,,::

ClK

NOTE: 1. SETlJP REQUIREMENTS FOR ASYNCHRONOUS

SIGNALS ONLY TO GUARANTEE RECOQNITION AT NEXT elK

REQUEST/GRANT SEQUENCE TIMING (MAXIMUM MODE ONLY)

~

1

Previousgranl

A1AA,~~!: |

| |

.... |

| |

~~ ,I | (SEE NOTE 1) | |

NOTE: 1. THE COPROCESSOR MAY NOT DRIVElHE BUSSES OUTSIDE THE REGION

•SHOWN WITHOUT InSKINO CONTENTION.

HOLD/HOLD ACKNOWLEDGE TIMING (MINIMUM MODE ONLy)

| 'ClKCYCLE- | ||

_I _'HVCH • (SEE NO'E" | |||

CLK ~ |

|

| |

HOlD~ |

| 1\ | |

|

| ||

|

| ||

HLOA |

|

| |

.... |

| TCLAZ | |

| COPROCESSOR | ||

61 |