iAPX 88/10

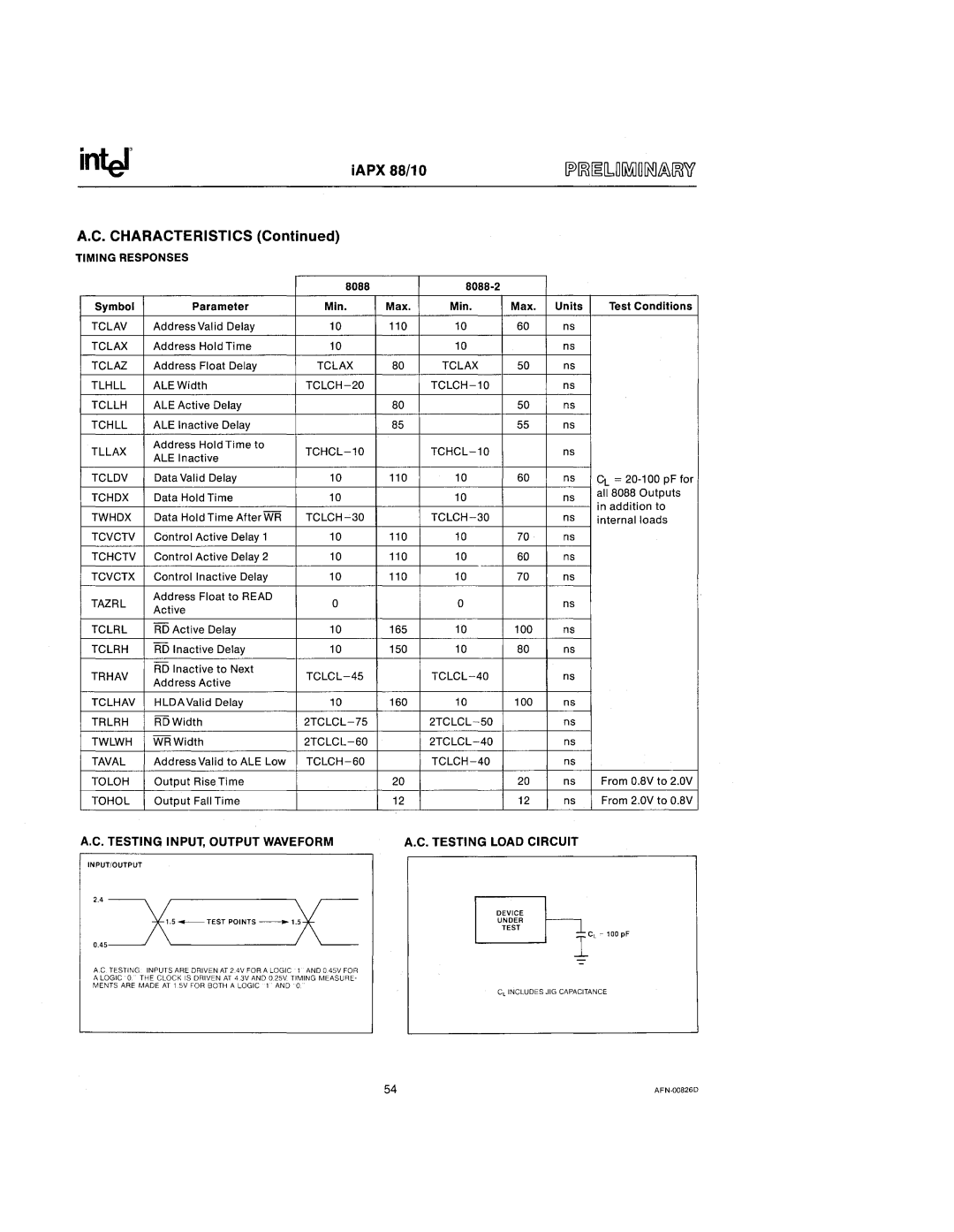

A.C. CHARACTERISTICS (Continued)

TIMING RESPONSES

Symbol | Parameter | |

TCLAV | AddressValid Delay | |

TCLAX | Address Hold Time | |

TCLAZ | Address Float Delay | |

TLHLL | ALE Width | |

TCLLH | ALE Active Delay | |

TCHLL | ALE Inactive Dell\Y | |

TLLAX | Address Hold Time to | |

ALE Inactive | ||

| ||

TCLDV | Data Valid Delay | |

TCHDX | Data Hold Time | |

TWHDX | Data Hold Time AfterWR | |

TCVCTV Control Active Delay 1 | ||

TCHCTV Control Active Delay 2 | ||

TCVCTX | Control Inactive Delay | |

TAZRL | Address Float to READ | |

Active | ||

| ||

TCLRL | RD Active Delay | |

TCLRH | RD Inactive Delay | |

TRHAV | RD Inactive to Next | |

Address Active | ||

| ||

TCLHAV | HLDAValid Delay | |

TRLRH | RDWidth | |

TWLWH | WRWidth | |

TAVAL | Address Valid to ALE Low | |

TOLOH | Output RiseTime | |

TOHOL | Output Fall Time | |

8088 |

| 8088·2 |

|

|

Min. | Max. | Min. | Max. | Units |

10 | 110 | 10 | 60 | ns |

10 |

| 10 |

| ns |

TCLAX | BO | TCLAX | 50 | ns |

|

| ns | ||

| BO |

| 50 | ns |

| B5 |

| 55 | ns |

|

| ns | ||

10 | 110 | 10 | 60 | ns |

10 |

| 10 |

| ns |

|

| ns | ||

10 | 110 | 10 | 70 | ns |

10 | 110 | 10 | 60 | ns |

10 | 110 | 10 | 70 | ns |

0 |

| 0 |

| ns |

10 | 165 | 10 | 100 | ns |

10 | 150 | 10 | BO | ns |

|

| ns | ||

10 | 160 | 10 | 100 | ns |

|

|

|

| ns |

|

|

|

| ns |

|

|

|

| ns |

| 20 |

| 20 | ns |

| 12 |

| 12 | ns |

Test Conditions

CL =

From O.BV to 2.0V

From 2.0V to O.BV

A.C. TESTIN~ INPUT, OUTPUT WAVEFORM | A.C. TESTING LOAD CIRCUIT |

INPUT/OUTPUT |

|

DEVICE I}

UNDER

TEST

CL=100 P F

":'

A.C TESTING: INPUTS ARE DRIVEN AT 2.4V FOR A LOGIC "1" AND 0 45V FOR

A LOGIC '0." THE CLOCK IS DRIVEN AT 4.3V AND 0 2SV. TIMING MEASURE-

MENTS ARE MADE AT 1.5V FOR BOTH A LOGIC 1" AND 0 '"

CL INCLUDES JIG CAPACITANCE

54 |