Contents

IAPX

Inter

Intel Corporation

About this Book

Page

Table of Contents

List of Figures

List of Figures

IAPX 88 VS. Zilog Z8D

Introduction To

Page

Chapter Introduction

Execution ~STRUCTION BUS

Bus Interface and Execution Units Work in Parallel

~~~11~~ks

Control Registers

Cal address Fig

Result is always 20-bits ofphysical address

13. Process Relocation

Displacement = 12 Wage Code Index

Instruction SET

Powerful String Processing

Conditional Transfers

Interfacing the 8088 is Easy Flexible

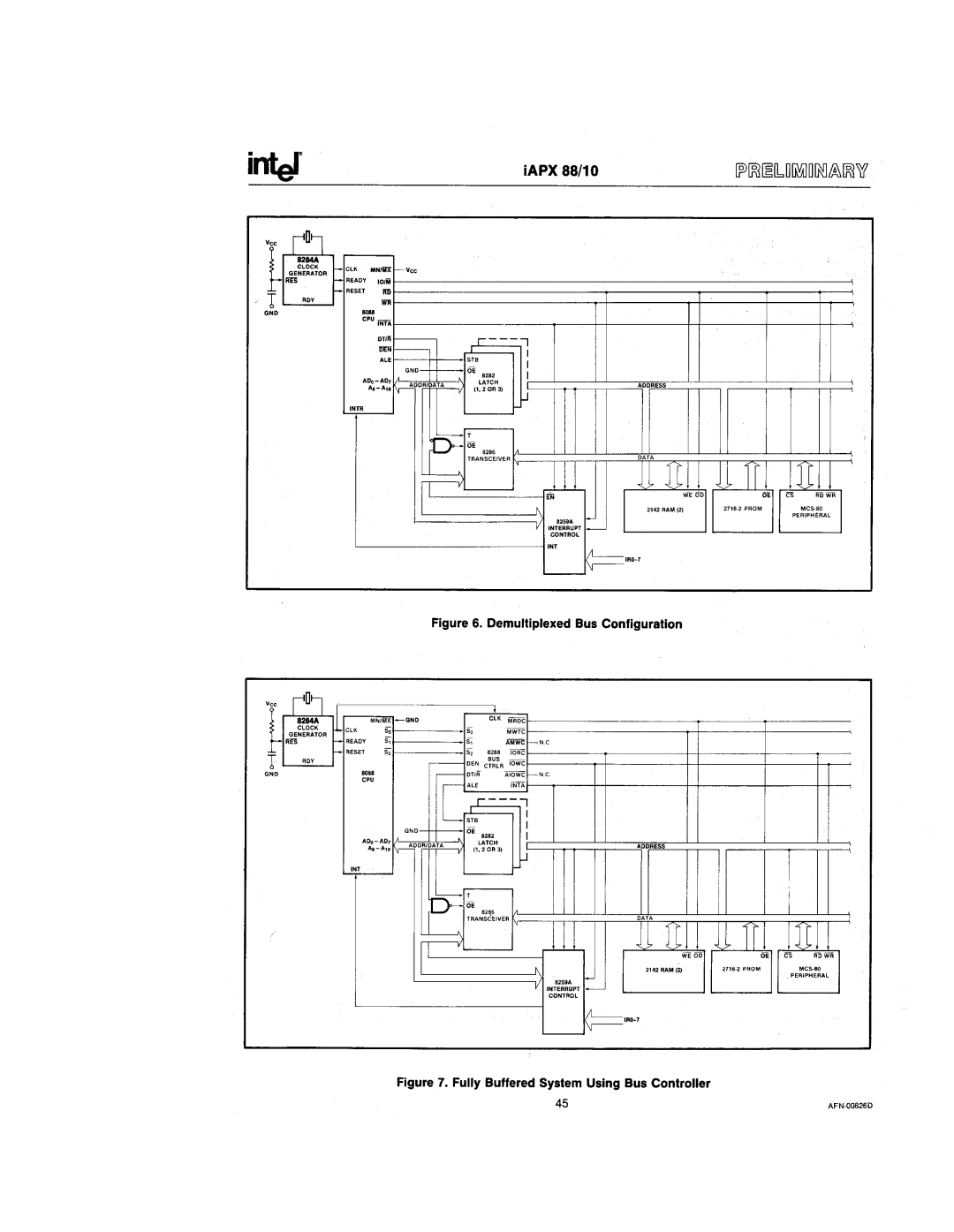

Using Special Multiplexed Bus Parts

\2~~~~\~~j-1L8~0~88~

To,ITovide extra drive capability for the data

IAPX 88 Performance is Cost Effective

Processor

Introduction Review

IAPX 188 CPU

Interrupt Controller

IAPX 188 CPU CPU Internal Registers

IAPX 88 Architecture Instructions

Page

Chapter

Architecture and Instructions

Data Registers Pointer and Index Registers

Flag Register File

Addressing Modes

==~TA~~=J

Direct Addressing

Fffffh

·--- 16 BITs----I.~1

Organization of the Instruction SET

Accumulator-Specific Transfers

Addition

Logic Instructions

Five primitive string oper~tions are provided

Body of this loop requires seven bytes of code

NMI

Instruction Timings

Assembly Language PROGRAMMING1

~g~~CE TRANSLATOR~g~bEECT

Inanqout Segment

MY Data Segment

Summary

Inandout Segment

Equal DB ?

INC CX increment CX

AL,PORTVAL OUT Portval and OFEH,AL

Assembler will assemble

Some examples are

Thing

Dontcare DB ?,?,?,?,?,?,?,?

Allzero DB 6 DUP

Then we could name first the byte in the word as follows

Segment Ends Assume

Mydata Segment Ends Myextra Alpha Beta Gamma Mystack

BL,X

Assume Dsnothing Cycle INC OLD~BYTE

Near and Far

Retstart

Cycle NIL INC AX

MOV AX,BX SI

Cmps BETA,ALPHA Scas Alpha Lods Alpha Stos Beta

Add two unpacked BCD Ascii strings together

Move 50 bytes between two overlapping strings

14. ASM-86 Reserved Words

14. ASM 86 Reserved Words

References For Instruction SET

Used Explanation

REF Referencesref For Instruction SET

Identifier Explanation

REF References REF For Instruction SET

Mod Field Bit Assignments

Page

AAA Ascii Adjust AAA For Addition

Operation Flags Affected

Ascii Adjust for Division

Description

Ascii Adjust AAM for Multiply

AAM

AAS Ascii Adjust AAS For Subtraction

1001111111

ADC ADD with Carry ADC

ADC destination, source

ADC ADD with Carry ADC

Additionadd

ADD destination,source

ADDCX, OX

Logical

Destination,source

Logical

BETA, 01H

Call Call Procedure Call

Call procedure-name

Call Call Procedure Call

CBW Convert Byte CBW Toword

1100110001

CLC Clear Carry

1111110001

Flag

1111111001

Enable Flag

Complement Carry Flag

1111101011

Comparecmp

CMP destination, source

CMP Compare

Immediate Operand with Accumulator

EM PS destination-string, source-string

Cmps Compare String Cmps Byte or Word

11010011wl

Rep

CWD Convert Word CWD To Doubleword

DAA Decimal Adjust DAA For Addition

DAS Decimal Adjust DAS For Subtraction

1001011111

DEC

DIV

Dividediv

DIV

Escape

ESC 20,AL

Halthlt

11110100

Idiv

Integer Divide Idiv

Integer Divide

Imul

Integer Multiply Imul

Input Byte or Word

Accumulator,port

Incrementinc

INC destination

Interrupt

INT interrupt-type

INT Interruptint

Encoding

1110011101

Iret Interrupt Return Iret

1110011111

Jump on Above Jumponnotbelow Or Equal

JNB

Jump on below Jump on not Above or Equal

Disp

JNA

Jump on Carry

Jcxz

Jcxz short-label

Jump on Equal

Jump on Zero

Jnle

Jump on Greater

JGE JNL

JGE Jump on Greater or Equal JNL Jump on not Less

Jump on Less Jumponnot Greater or Equal

JLE

JNG Jump on not Greater

JMP Jump Unconditionally JMP

JMP target

MP Jump Unconditionally JMP

JNC Jump on not Carry JNC

JNE JNZ

JNE Jump on not Equal JNZ Jump on not Zero

Jump on not Overflow

Jump on not Sign

JNP JPO

JNP Jump on not Parity JPO Jump on Parity ODD

Jump on Overflow JO

JPE

Jump on Sign

Lahf Load Register AH Lahf From Flags

111 0001 01 1mod reg rIm

LOS destination,source

Load Effective Address

LEA destination,source

Load Pointer Using ES LES

LES destination, source

Lock Lock the BUS Lock

Lods source-string

Lods Load String Lods Byte or Word

11010110wl

Loop Looploop

Loop short-label

Loopwhile Equal Zero

LOOPE/LOOPZ short-label

Loopwhile

LOOPNE/LOOPNZ short-label

11100011 w 1 mod 000 rim 1 data

MOV Movebyteorword MOV

110001 0 d w 1mod reg rim

0 1 1 w reg I· data

11 00011 00 Imod 0 reg r I ml

MOV Move Byte or Word MOV

11000111 0 Imod 0 reg r/ml

Movs destination-string, source-string

Movs Move String Movs

11010010wl

Multiplymul

MUL source

NEG destination

Negateneg

11111 011 w 1mod a11 rIm

No Operation

1100100001

Not destination

Logical not not

11111 01 1 w 1mod 0 1 0 rim

Logical or

Or destination,source

Or AL, BL

11110111wl

Outputout

1111 00 11 w 1 port

1014

Poppop

POP destination

POP POP

POP Flags Popf

All

Push Pushpush

01 01 0 reg

Pushpush

111111111 1mod 11 0 rIm

10 0 0 reg 1 1 0

Pushf

RCL Rotate Through RCL Carry Left

RCL destination, count

RCL Rotate Through RCL

Carry Right

RCR destination, count

Repeat While Equal Repeat While Zero

Repeat While not Equal Repeat While not Zero

Repeat While Equal Repeat While Zero

Repeat While not Equal Repeat While not Zero

Repeat While not Equal Repeatwhile not Zero

1111001Z

Returnret

RET optional-pap-value

1110010111

1110000111

11 1 00001 0 1 data-low

ROL Rotate Left ROL

ROL destination, count

Rotate Right ROR

ROR destination, count

Sahf Store Register AH Sahf Into Flags

1100111101

SAL Shift Arithmetic Left SHL Shift Logical Left

CF, OF, PF, SF, ZF

SAL SHL

Shift Arithmetic Left Shift Logical Left

SAR Shift Arithmetic SAR Right

CF, OF, PF, SF, ZF

SAR Operands Clocks Transfers Bytes SAR Coding Example

Subtract with Borrow

See destination,source

SBB

SeAS destination-string

Scas Scan Byte or Scas Word String

11010111wl

+ 1519/rep

SHR Shift Logical Right SHR

SHR destination, source

111 01 00 v w 1mod 1 01 rIm

If v = 0 then Count = 1 else Count = CL

SET Carry

1111110011

STD SET Direction Flag STD

1111111011

SET INTERRUPT· Enable Flag

Stos destination-string

Stos Store BYTE/OR/ Stos Word String

11010101wl

Subtractsub

SUB destination,source

SUB Subtractsub

Testtest

Test destination,source

11 0 1 0 1 0 0 w 1 data

1100001 0 w 1mod reg rIm

11111 011 w 1 mod 000 rIm 1 data

Waitwait

1100110111

Exchange Xchg

Xchg destination, source

11000011 w 1mod reg rIm

001 0 reg

11010111

Xlat translate-table

Exclusive or XOR

XOR destination,source

XORCX, BX

Page

IAPX Hardware Design

Page

Hardware Design

Hardware Design

Timing

~11 ttttt

+- Reset

Bus Timing and Minimum Mode Status

\L- -----tl

Bus Interface

Memory and Peripheral Interface

ROl

~Atui

Hold 101M

8284A

FFFFOH·

Inputs VIH of 2.6 volts

DV Ie dT = C

ElK

Ready Output

RDYINPUT~~

8284A

External Interrupts

3FFH

Internal Interrupts

SINGLE-STEP Execution

Bus Control Transfer

~E~ ~

ClK

31. Minimum/Maximum Mode

Osa

Pulse PULS.E..2

KJC

Page

Application4 Examples

Page

Chapter Application Examples

RESfrF 0J

110~

Address Line Usage Recommended Device Addressing

~RESET

~~~--~~3-=

~~~~~~~~~~~~5~AD1g

~ ~ NC

Rr? -=

Data character or a controlIstatus char- acter

Ururururu

Ttj

~rt~27

IAPX 88-BASED $100 BUS System

Language

8088

IAPX 88 Multiprocessor Interface

Cfi

~ ~I~

Application Examples

~o,es

···l-T...-lfl

~--i

Page

Supplement

Page

Microcomputer Overview

Supplement

Machine Cycles

Whatsinside the CPU?

Addressing modes

Page

AppendixA

Benchmark Report Intel iAPX 88 vs Zilog Z80

Processor Description

Appendix

Performance Measurements

Block Move

Interrupt Response

I2.6

Z80/iAPX

Memory Utilization Bytes iAPX 88 vs Z80 Bytes of Code

Conclusion

Page

Appendix Benchmark Program Code and Flowcharts

Usage

LPI HL,O

Block Translate Flowchart

Ebcbuf

DE ,EBCBUF

Bubble Sort

Accumulator

Zao

Benchmark Report Intel iAPX 88 vs Motorola MC6809

Processor Description

IAPX

Program Descriptions

Results

MC6809

IAPX 88/10

Appendix

Appendix Benchmark Program Code and Flowcharts

P1,AX

Addd

Block Move Flowchart

Register Usage

Register Usage

Character Search Flowchart

OI,PTR

Usage Accumulator Count

Inter

IAPX 88/10

Inter

IAPX 88/10

Inter

~ Xxxxoh

AFN-OOB26D

TI IT

Ill

UP&=1? ~

External Interface

Halt

IAPX 88/10 External Synchronization via Test

AFN-008260

Inter

Absolute Maximum RATINGS·

IAPX 88/10

IAPX 88/10 Characteristics

~--~~

IAPX 88/10 Waveforms

IAPX 88/10

Characteristics

~Ii

Inter

1L.~~

Instruction SET Summary

Inter

8284A Clock Generator and Driver for iAPX 86, 88 Processors

IntJ8284A

+---H D

8284A

Characteristics

~/~----------~t

8284A

Vcc

Inter

Inter

Absolute Maximum RATINGS·

Inter8282/8283

\V\1

8286/8287

8286/8287

~,,o

Inter8286/8287

IntJ8286/8287

Domestic Sales Offices

European Sales Offices

International Sales Offices