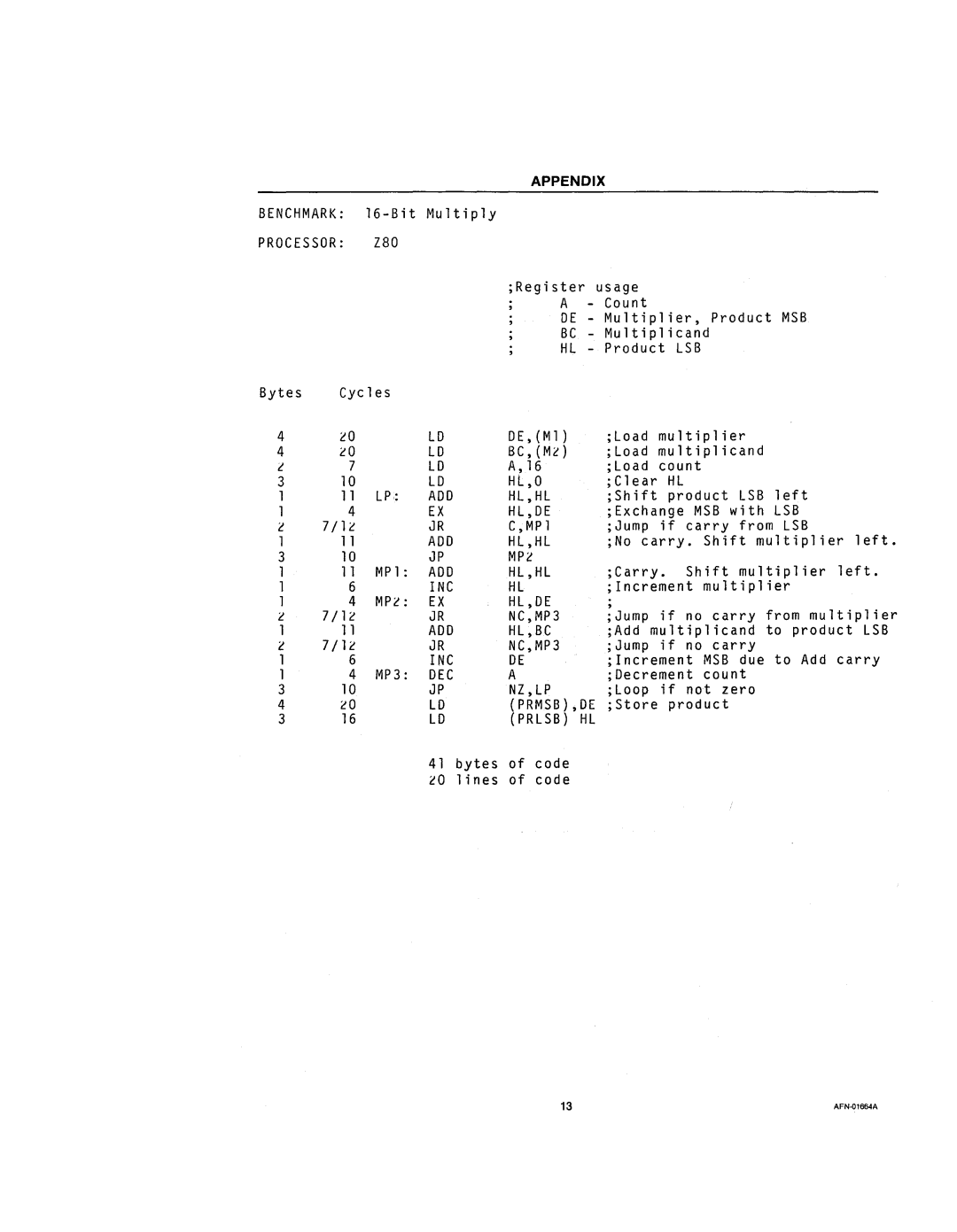

APPENDIX

BENCHMARK:

PROCESSOR: Z80

;Register | usage |

A | Count |

DE | Multiplier, Product MSB |

BC | Multiplicand |

HL | Product LSB |

Bytes Cycles

4 | ~O |

| LD |

| DE,(Ml) | ;Load | multiplier |

| |||

4 | ~O |

| LD |

| BC, (M~) | ;Load | multiplicand |

| |||

t | 7 |

| LD |

| A,16 | ;Load | count |

|

| ||

3 | 10 | LPI: | LD |

| HL,O | ;Clear | HL |

| LSB | left | |

1 | 11 | ADD |

| HL,HL | ;Shift | product | |||||

1 | 4 |

| EX |

| HL,DE | ;Exchange | MSB | with | LSB | ||

~ | 71lt |

| JR |

| C,MPl | ;Jump if carry from LSB | |||||

1 | 11 |

| ADD |

| HL,HL | ;No carry. Shift multiplier left. | |||||

3 | 10 |

| JP |

| MP~ |

| ;Carry. | Shift | multiplier left. | ||

1 | 11 | MP 1: | ADD |

| HL,HL | ||||||

1 | 6 | MPt: | INC |

| HL |

| ;Increment multiplier | ||||

1 | 4 | EX |

| HL,DE | ; |

|

|

|

| ||

~ | 7Il ~ |

| JR |

| NC,MP3 | ;Jump if no carry from multiplier | |||||

1 | 11 |

| ADD |

| HL,BC | ;Add multiplicand to product LSB | |||||

~ | 71l~ |

| JR |

| NC,MP3 | ;Jump | if | no carry |

| ||

1 | 6 | MP3: | INC |

| DE |

| ;Increment MSB due to Add carry | ||||

1 | 4 | DEC |

| A |

| ;Decrement count |

| ||||

3 | 10 |

| JP |

| NZ,LP | ;Loop | if | not zero |

| ||

4 | ~O |

| LD |

| (PRMSB),DE | ;Store | product |

|

| ||

3 | 16 |

| LD |

| (PRLSB) HL |

|

|

|

|

| |

|

|

| 41 | bytes | of | code |

|

|

|

|

|

|

|

| ~O | lines | of | code |

|

|

|

|

|

13 |