HARDWARE DESIGN

This signal floats to

INTR. Interrupt Request is a

When INTR is detected HIGH, the 8088 jumps to an interrupt service routine via an interrupt vector table in system memory.

INTR can be internally masked through software by resetting the interrupt enable bit in the Flag register. INTR is internally synchronized.

INTA. Used as a read strobe during interrupt acknowledge cycles, INTA is active· LOW during T2, T3, and T4 of each interrupt acknowledge cycle. INTA is never floated.

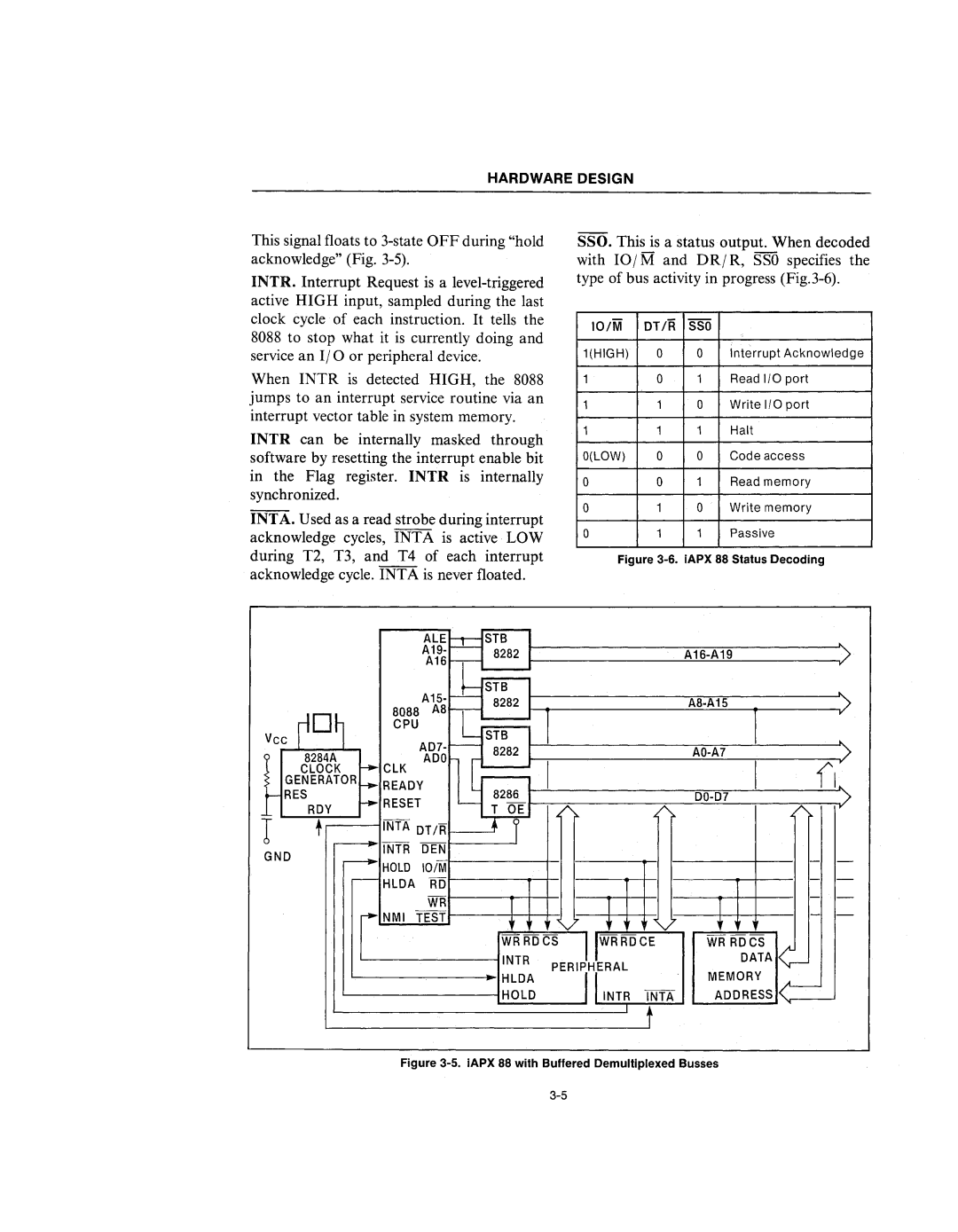

880.This is a status output. When decoded with IO I M and D RI R, SSO specifies the type of bus activity in progress

IO/iiii | OT/R | 550 |

|

1(HIGH) | 0 | 0 | Interrupt Acknowledge |

1 | 0 | 1 | Read 1/0 port |

1 | 1 | 0 | Write 1/0 port |

1 | 1 | 1 | Halt |

O(lOW) | 0 | 0 | Code access |

0 | 0 | 1 | Read memory |

0 | 1 | 0 | Write memory |

0 | 1 | 1 | Passive |

Figure 3-6. iAPX 88 Status Decoding

|

|

|

|

| ALE | STB |

|

|

|

|

|

|

|

|

|

| A19- | 8282 | I |

|

|

| |

|

|

|

|

| A16 |

|

|

| |||

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

| A15- | STB |

|

|

|

| ) |

|

|

|

| 8088 | 8282 | I |

|

| |||

| D |

| A8 |

|

|

|

|

|

| ||

|

| CPU |

| STB |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| |||

Vec | r | 1 |

| AD7- | 8282 | I |

|

| |||

I | 8284A |

| ADO |

|

|

|

| I | |||

| CLOCK |

|

|

|

| I |

| ||||

GENERATOR |

| I |

| ||||||||

~ RES |

|

|

| 8286·1 |

|

|

| ||||

I | ROY |

|

| T OEI | A | A |

| A | |||

+ |

|

| INTA DT/A" | • r |

|

|

|

|

| ||

|

|

|

|

|

|

|

|

| |||

GND |

|

|

| INTR | DEN |

|

|

|

| - | |

|

|

| ~ HOLD | 101M |

|

|

|

|

| ||

|

|

| - | HLDA | RD |

|

|

| ,I | ,I | - |

|

|

|

|

|

|

| - | ||||

|

|

|

| ,.. NMI TEST | " I |

|

| ||||

|

|

|

|

|

| - | |||||

|

|

|

|

| WR |

|

|

|

|

|

|

|

|

|

|

|

| WRRDCS | J.IWRRDCE | WR RDCS | I<=- | ||

|

|

|

|

|

|

|

|

| If | MEMORY | |

|

|

|

|

|

| HLDA |

| DATA |

| ||

|

|

|

|

|

| INTR | PERIPHERAL | ADDRESS 1<== | |||

|

|

|

|

|

| HOLD |

| INTR INTA | |||

|

|

|

|

|

|

|

|

| t |

|

|