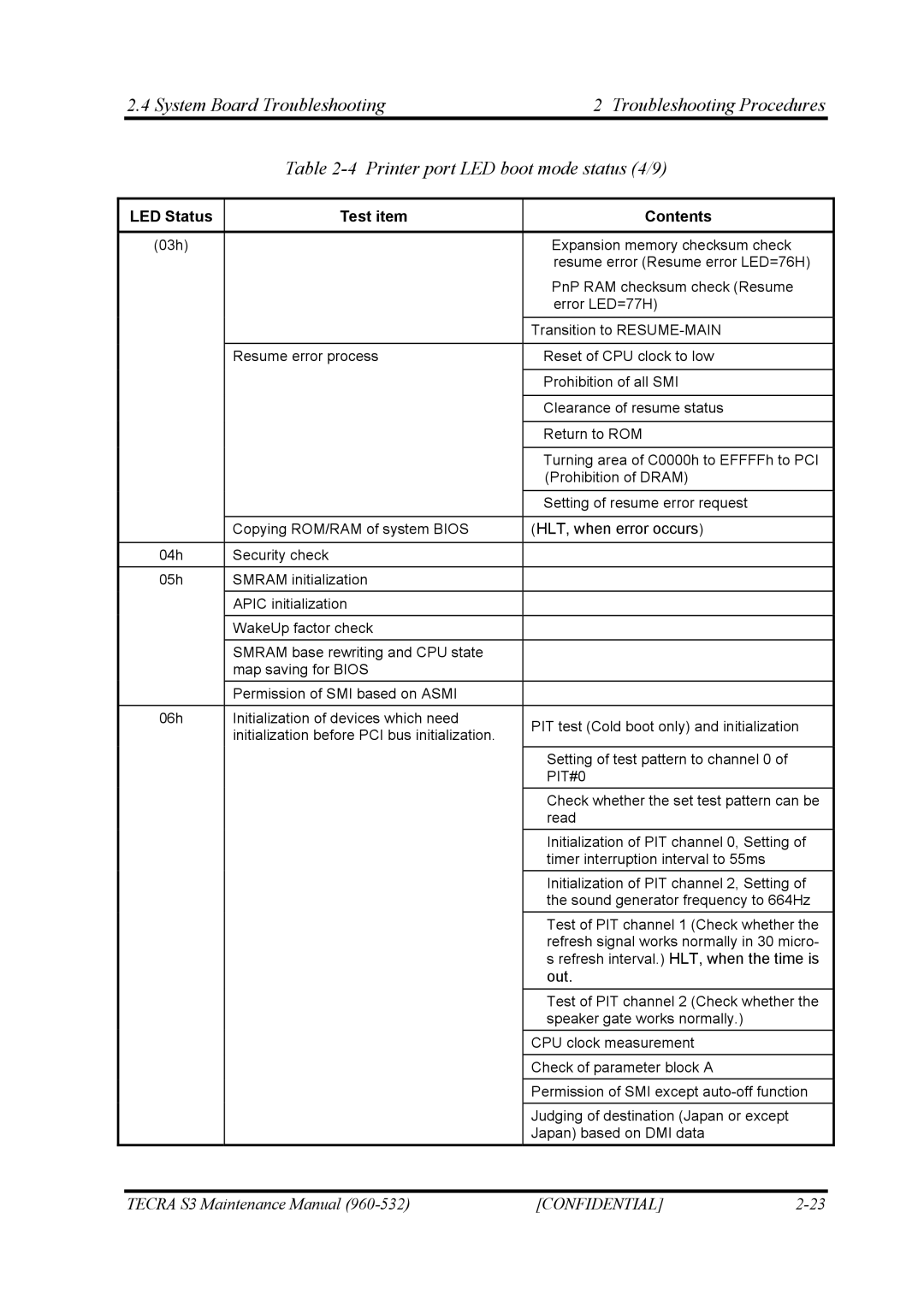

2.4 System Board Troubleshooting | 2 Troubleshooting Procedures |

Table

LED Status | Test item | Contents |

|

|

|

(03h) |

| Expansion memory checksum check |

|

| resume error (Resume error LED=76H) |

|

| PnP RAM checksum check (Resume |

|

| error LED=77H) |

|

|

|

|

| Transition to |

|

|

|

| Resume error process | Reset of CPU clock to low |

|

|

|

|

| Prohibition of all SMI |

|

|

|

|

| Clearance of resume status |

|

|

|

|

| Return to ROM |

|

|

|

|

| Turning area of C0000h to EFFFFh to PCI |

|

| (Prohibition of DRAM) |

|

|

|

|

| Setting of resume error request |

|

|

|

| Copying ROM/RAM of system BIOS | (HLT, when error occurs) |

|

|

|

04h | Security check |

|

05h | SMRAM initialization |

|

| APIC initialization |

|

| WakeUp factor check |

|

|

|

|

| SMRAM base rewriting and CPU state |

|

| map saving for BIOS |

|

| Permission of SMI based on ASMI |

|

06h | Initialization of devices which need | PIT test (Cold boot only) and initialization |

| initialization before PCI bus initialization. | |

|

| |

|

| Setting of test pattern to channel 0 of |

|

| PIT#0 |

|

| Check whether the set test pattern can be |

|

| read |

|

| Initialization of PIT channel 0, Setting of |

|

| timer interruption interval to 55ms |

|

| Initialization of PIT channel 2, Setting of |

|

| the sound generator frequency to 664Hz |

|

| Test of PIT channel 1 (Check whether the |

|

| refresh signal works normally in 30 micro- |

|

| s refresh interval.) HLT, when the time is |

|

| out. |

|

| Test of PIT channel 2 (Check whether the |

|

| speaker gate works normally.) |

|

| CPU clock measurement |

|

| Check of parameter block A |

|

| Permission of SMI except |

|

| Judging of destination (Japan or except |

|

| Japan) based on DMI data |

TECRA S3 Maintenance Manual | [CONFIDENTIAL] |