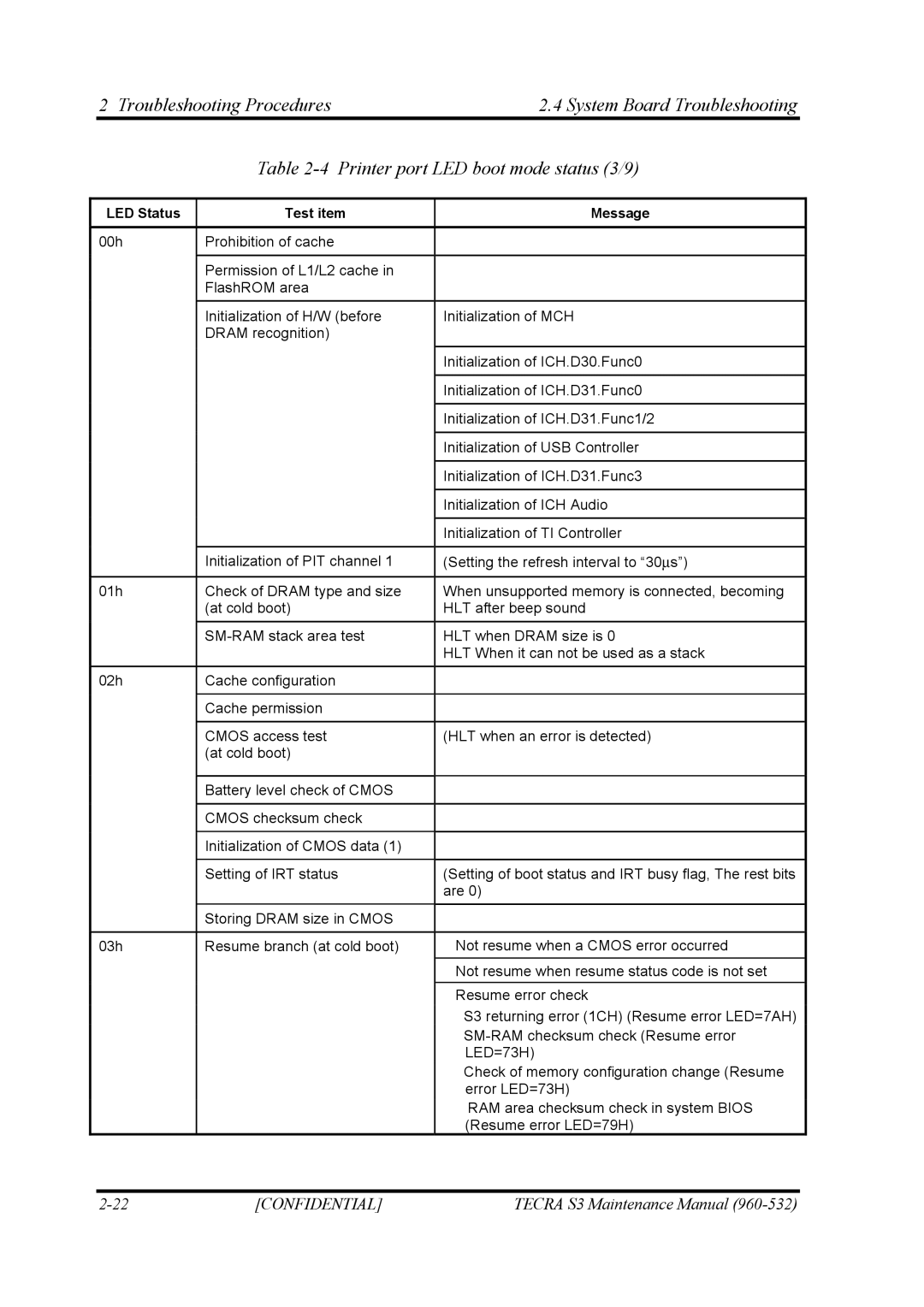

2 Troubleshooting Procedures | 2.4 System Board Troubleshooting |

Table

LED Status | Test item | Message |

|

|

|

00h | Prohibition of cache |

|

|

|

|

| Permission of L1/L2 cache in |

|

| FlashROM area |

|

| Initialization of H/W (before | Initialization of MCH |

| DRAM recognition) |

|

|

| Initialization of ICH.D30.Func0 |

|

|

|

|

| Initialization of ICH.D31.Func0 |

|

|

|

|

| Initialization of ICH.D31.Func1/2 |

|

|

|

|

| Initialization of USB Controller |

|

|

|

|

| Initialization of ICH.D31.Func3 |

|

|

|

|

| Initialization of ICH Audio |

|

|

|

|

| Initialization of TI Controller |

|

|

|

| Initialization of PIT channel 1 | (Setting the refresh interval to “30∝s”) |

|

|

|

01h | Check of DRAM type and size | When unsupported memory is connected, becoming |

| (at cold boot) | HLT after beep sound |

|

|

|

| HLT when DRAM size is 0 | |

|

| HLT When it can not be used as a stack |

|

|

|

02h | Cache configuration |

|

|

|

|

| Cache permission |

|

|

|

|

| CMOS access test | (HLT when an error is detected) |

| (at cold boot) |

|

|

|

|

| Battery level check of CMOS |

|

|

|

|

| CMOS checksum check |

|

|

|

|

| Initialization of CMOS data (1) |

|

|

|

|

| Setting of IRT status | (Setting of boot status and IRT busy flag, The rest bits |

|

| are 0) |

| Storing DRAM size in CMOS |

|

|

|

|

03h | Resume branch (at cold boot) | Not resume when a CMOS error occurred |

|

| Not resume when resume status code is not set |

|

| Resume error check |

|

| S3 returning error (1CH) (Resume error LED=7AH) |

|

| |

|

| LED=73H) |

|

| Check of memory configuration change (Resume |

|

| error LED=73H) |

|

| RAM area checksum check in system BIOS |

|

| (Resume error LED=79H) |

[CONFIDENTIAL] | TECRA S3 Maintenance Manual |