DS33Z41

Quad IMUX Ethernet Mapper

GENERAL DESCRIPTION

The DS33Z41 extends a 10/100 Ethernet LAN segment by encapsulating MAC frames in HDLC or X.86 (LAPS) for transmission over up to four interleaved PDH/TDM data streams using robust, balanced, and programmable inverse multiplexing. The Interleave Bus (IBO) serial link supports seamless bidirectional interconnection with Dallas Semiconductor’s T1/E1 framers and transceivers.

The device performs

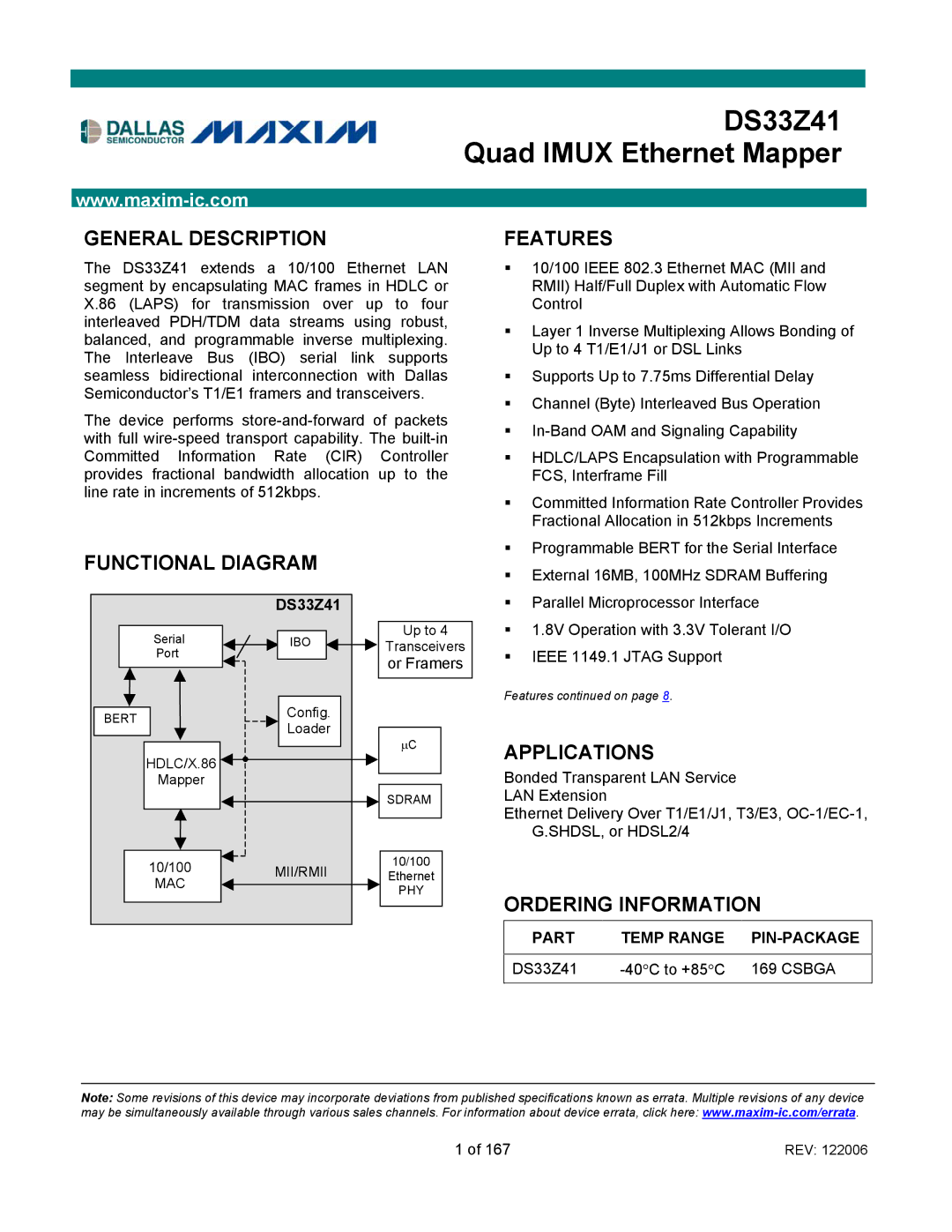

FUNCTIONAL DIAGRAM

| DS33Z41 |

| |

Serial | IBO | Up to 4 | |

Transceivers | |||

Port | |||

| or Framers | ||

|

| ||

BERT | Config. |

| |

Loader |

| ||

| µC | ||

|

| ||

HDLC/X.86 |

|

| |

Mapper |

|

| |

|

| SDRAM | |

10/100 | MII/RMII | 10/100 | |

Ethernet | |||

MAC |

| PHY | |

|

|

FEATURES

10/100 IEEE 802.3 Ethernet MAC (MII and RMII) Half/Full Duplex with Automatic Flow Control

Layer 1 Inverse Multiplexing Allows Bonding of Up to 4 T1/E1/J1 or DSL Links

Supports Up to 7.75ms Differential Delay Channel (Byte) Interleaved Bus Operation

HDLC/LAPS Encapsulation with Programmable FCS, Interframe Fill

Committed Information Rate Controller Provides Fractional Allocation in 512kbps Increments

Programmable BERT for the Serial Interface External 16MB, 100MHz SDRAM Buffering Parallel Microprocessor Interface

1.8V Operation with 3.3V Tolerant I/O IEEE 1149.1 JTAG Support

Features continued on page 8.

APPLICATIONS

Bonded Transparent LAN Service

LAN Extension

Ethernet Delivery Over T1/E1/J1, T3/E3,

G.SHDSL, or HDSL2/4

ORDERING INFORMATION

PART | TEMP RANGE | |

|

|

|

DS33Z41 | 169 CSBGA | |

|

|

|

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here:

1 of 167 | REV: 122006 |