DS33Z41 Quad IMUX Ethernet Mapper

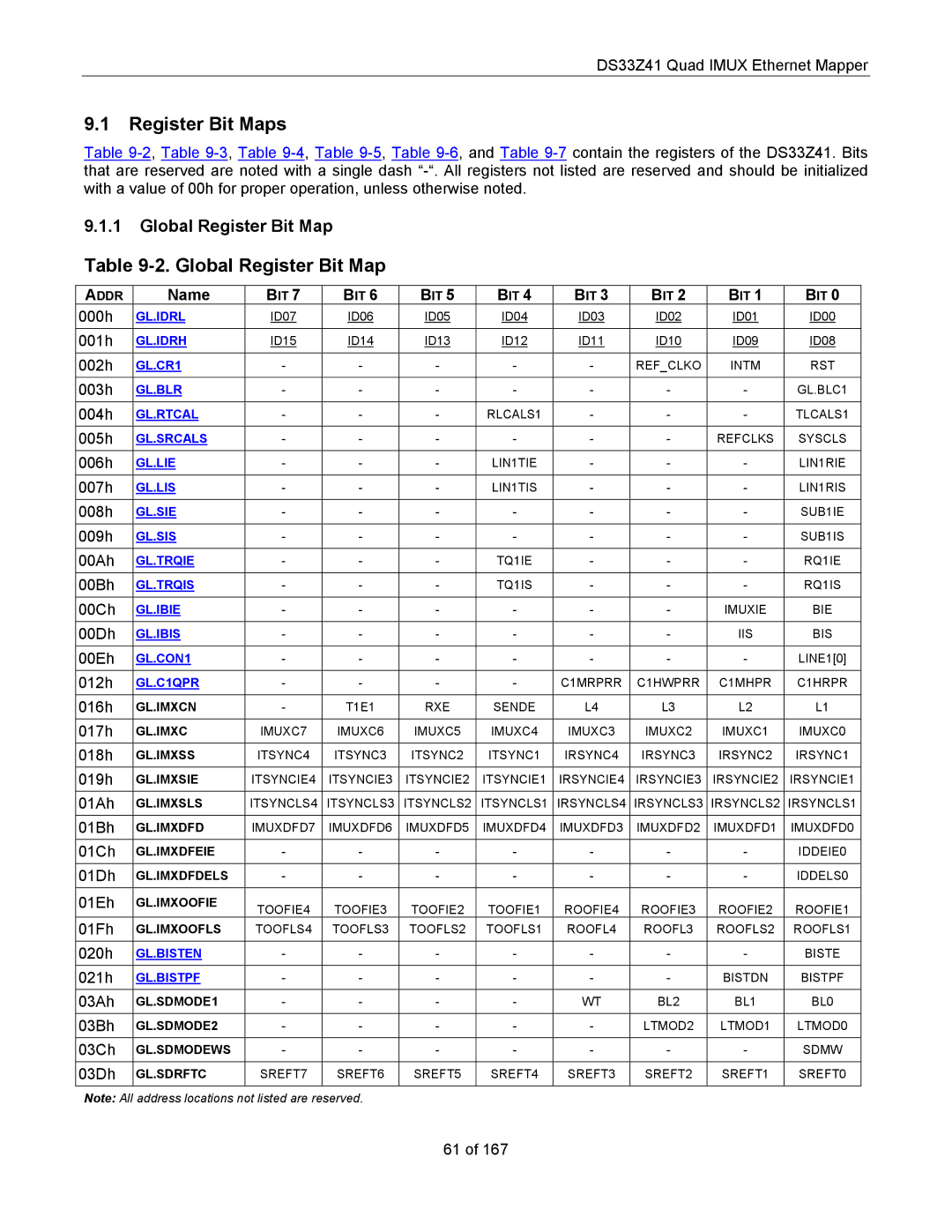

9.1Register Bit Maps

Table

9.1.1Global Register Bit Map

Table 9-2. Global Register Bit Map

ADDR | Name | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

000h | GL.IDRL | ID07 | ID06 | ID05 | ID04 | ID03 | ID02 | ID01 | ID00 |

001h | GL.IDRH | ID15 | ID14 | ID13 | ID12 | ID11 | ID10 | ID09 | ID08 |

002h | GL.CR1 | - | - | - | - | - | REF_CLKO | INTM | RST |

003h | GL.BLR | - | - | - | - | - | - | - | GL.BLC1 |

004h | GL.RTCAL | - | - | - | RLCALS1 | - | - | - | TLCALS1 |

005h | GL.SRCALS | - | - | - | - | - | - | REFCLKS | SYSCLS |

006h | GL.LIE | - | - | - | LIN1TIE | - | - | - | LIN1RIE |

007h | GL.LIS | - | - | - | LIN1TIS | - | - | - | LIN1RIS |

008h | GL.SIE | - | - | - | - | - | - | - | SUB1IE |

009h | GL.SIS | - | - | - | - | - | - | - | SUB1IS |

00Ah | GL.TRQIE | - | - | - | TQ1IE | - | - | - | RQ1IE |

00Bh | GL.TRQIS | - | - | - | TQ1IS | - | - | - | RQ1IS |

00Ch | GL.IBIE | - | - | - | - | - | - | IMUXIE | BIE |

00Dh | GL.IBIS | - | - | - | - | - | - | IIS | BIS |

00Eh | GL.CON1 | - | - | - | - | - | - | - | LINE1[0] |

012h | GL.C1QPR | - | - | - | - | C1MRPRR | C1HWPRR | C1MHPR | C1HRPR |

016h | GL.IMXCN | - | T1E1 | RXE | SENDE | L4 | L3 | L2 | L1 |

017h | GL.IMXC | IMUXC7 | IMUXC6 | IMUXC5 | IMUXC4 | IMUXC3 | IMUXC2 | IMUXC1 | IMUXC0 |

018h | GL.IMXSS | ITSYNC4 | ITSYNC3 | ITSYNC2 | ITSYNC1 | IRSYNC4 | IRSYNC3 | IRSYNC2 | IRSYNC1 |

019h | GL.IMXSIE | ITSYNCIE4 | ITSYNCIE3 | ITSYNCIE2 | ITSYNCIE1 | IRSYNCIE4 | IRSYNCIE3 | IRSYNCIE2 | IRSYNCIE1 |

01Ah | GL.IMXSLS | ITSYNCLS4 | ITSYNCLS3 | ITSYNCLS2 | ITSYNCLS1 | IRSYNCLS4 | IRSYNCLS3 | IRSYNCLS2 | IRSYNCLS1 |

01Bh | GL.IMXDFD | IMUXDFD7 | IMUXDFD6 | IMUXDFD5 | IMUXDFD4 | IMUXDFD3 | IMUXDFD2 | IMUXDFD1 | IMUXDFD0 |

01Ch | GL.IMXDFEIE | - | - | - | - | - | - | - | IDDEIE0 |

01Dh | GL.IMXDFDELS | - | - | - | - | - | - | - | IDDELS0 |

01Eh | GL.IMXOOFIE | TOOFIE4 | TOOFIE3 | TOOFIE2 | TOOFIE1 | ROOFIE4 | ROOFIE3 | ROOFIE2 | ROOFIE1 |

|

| ||||||||

01Fh | GL.IMXOOFLS | TOOFLS4 | TOOFLS3 | TOOFLS2 | TOOFLS1 | ROOFL4 | ROOFL3 | ROOFLS2 | ROOFLS1 |

020h | GL.BISTEN | - | - | - | - | - | - | - | BISTE |

021h | GL.BISTPF | - | - | - | - | - | - | BISTDN | BISTPF |

03Ah | GL.SDMODE1 | - | - | - | - | WT | BL2 | BL1 | BL0 |

03Bh | GL.SDMODE2 | - | - | - | - | - | LTMOD2 | LTMOD1 | LTMOD0 |

03Ch | GL.SDMODEWS | - | - | - | - | - | - | - | SDMW |

03Dh | GL.SDRFTC | SREFT7 | SREFT6 | SREFT5 | SREFT4 | SREFT3 | SREFT2 | SREFT1 | SREFT0 |

Note: All address locations not listed are reserved.

61 of 167