DS33Z41 Quad IMUX Ethernet Mapper

9.5Serial Interface Registers

The Serial Interface contains the Serial HDLC transport circuitry and the associated serial port. The Serial Interface register map consists of registers that are common functions, transmit functions, and receive functions.

Bits that are underlined are

Counter registers are updated by asserting (low to high transition) the associated performance monitoring update signal (xxPMU). During the counter register update process, the associated performance monitoring status signal (xxPMS) is deasserted. The counter register update process consists of loading the counter register with the current count, resetting the counter, forcing the zero count status indication low for one clock cycle, and then asserting xxPMS. No events are missed during this update procedure.

A latched bit is set when the associated event occurs, and remains set until it is cleared by reading. Once cleared, a latched bit will not be set again until the associated event occurs again. Reserved configuration bits and registers should be written to zero.

9.5.1Serial Interface Transmit and Common Registers

Serial Interface Transmit Registers are used to control the HDLC transmitter associated with each Serial Interface. The register map is shown in the following Table. Note that throughout this document the HDLC Processor is also referred to as a “packet processor”.

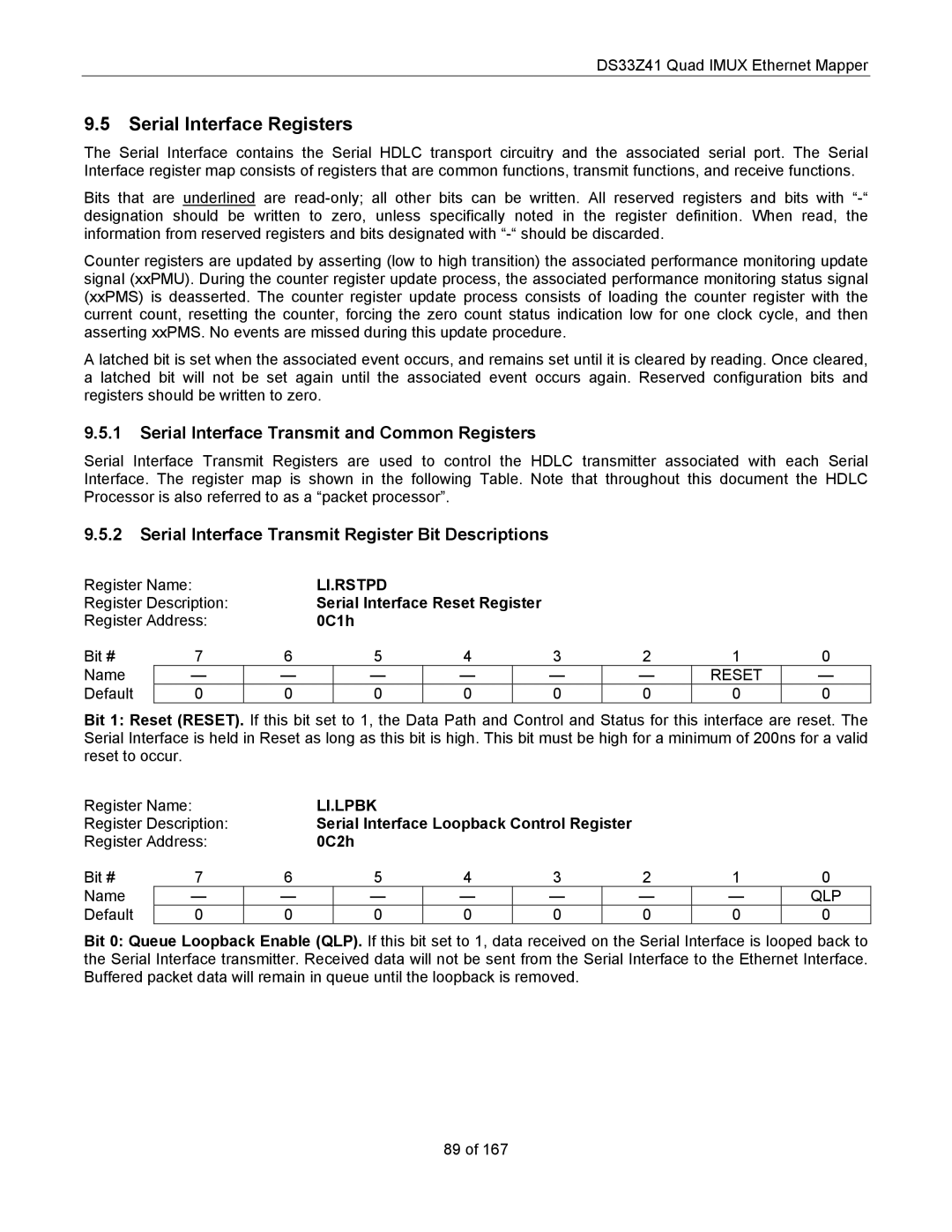

9.5.2Serial Interface Transmit Register Bit Descriptions

Register Name: |

| LI.RSTPD |

|

|

|

|

|

| ||

Register Description: |

| Serial Interface Reset Register |

|

|

|

| ||||

Register Address: |

| 0C1h |

|

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 |

| 3 | 2 | 1 | 0 | |

Name | — | — |

| — | — |

| — | — | RESET | — |

Default | 0 | 0 |

| 0 | 0 |

| 0 | 0 | 0 | 0 |

Bit 1: Reset (RESET). If this bit set to 1, the Data Path and Control and Status for this interface are reset. The Serial Interface is held in Reset as long as this bit is high. This bit must be high for a minimum of 200ns for a valid reset to occur.

Register Name: |

| LI.LPBK |

|

|

|

|

|

| ||

Register Description: |

| Serial Interface Loopback Control Register |

|

|

| |||||

Register Address: |

| 0C2h |

|

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 |

| 2 | 1 | 0 | |

Name | — | — |

| — | — | — |

| — | — | QLP |

Default | 0 | 0 |

| 0 | 0 | 0 |

| 0 | 0 | 0 |

Bit 0: Queue Loopback Enable (QLP). If this bit set to 1, data received on the Serial Interface is looped back to the Serial Interface transmitter. Received data will not be sent from the Serial Interface to the Ethernet Interface. Buffered packet data will remain in queue until the loopback is removed.

89 of 167