DS33Z41 Quad IMUX Ethernet Mapper

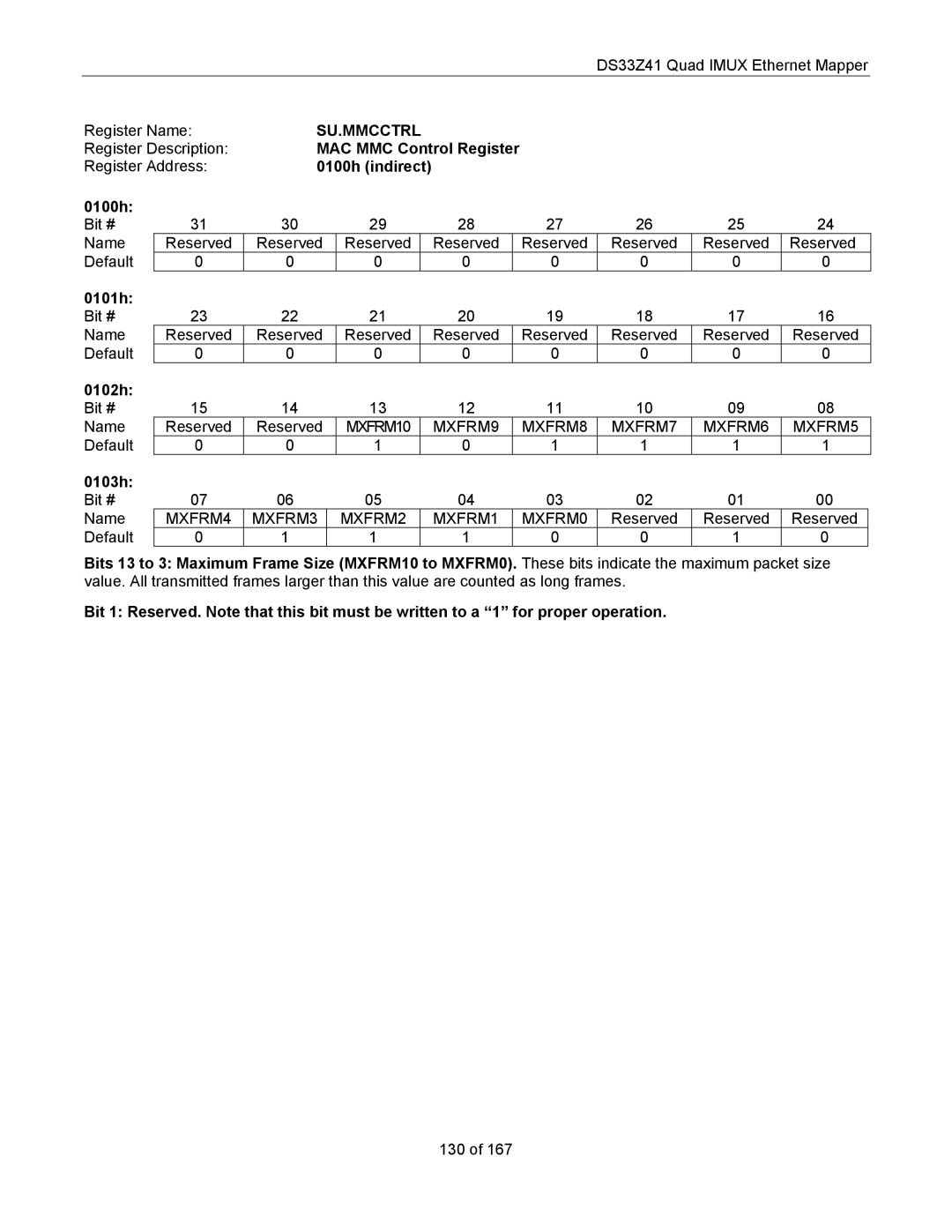

Register Name: | SU.MMCCTRL |

|

|

|

|

|

|

| ||||

Register Description: | MAC MMC Control Register |

|

|

|

|

| ||||||

Register Address: | 0100h (indirect) |

|

|

|

|

|

|

| ||||

0100h: |

|

|

|

|

|

|

|

|

|

|

|

|

Bit # | 31 | 30 |

| 29 |

| 28 |

| 27 | 26 | 25 | 24 |

|

Name | Reserved | Reserved | Reserved |

| Reserved |

| Reserved | Reserved | Reserved | Reserved | ||

Default | 0 | 0 |

| 0 |

| 0 |

| 0 | 0 | 0 | 0 |

|

0101h: |

|

|

|

|

|

|

|

|

|

|

|

|

Bit # | 23 | 22 |

| 21 |

| 20 |

| 19 | 18 | 17 | 16 |

|

Name | Reserved | Reserved | Reserved |

| Reserved |

| Reserved | Reserved | Reserved | Reserved | ||

Default | 0 | 0 |

| 0 |

| 0 |

| 0 | 0 | 0 | 0 |

|

0102h: |

|

|

|

|

|

|

|

|

|

|

|

|

Bit # | 15 | 14 |

| 13 |

| 12 |

| 11 | 10 | 09 | 08 |

|

Name | Reserved | Reserved | MXFRM10 |

| MXFRM9 |

| MXFRM8 | MXFRM7 | MXFRM6 | MXFRM5 | ||

Default | 0 | 0 |

| 1 |

| 0 |

| 1 | 1 | 1 | 1 |

|

0103h: |

|

|

|

|

|

|

|

|

|

|

|

|

Bit # | 07 | 06 |

| 05 |

| 04 |

| 03 | 02 | 01 | 00 |

|

Name | MXFRM4 | MXFRM3 |

| MXFRM2 |

| MXFRM1 |

| MXFRM0 | Reserved | Reserved | Reserved |

|

Default | 0 | 1 |

| 1 |

| 1 |

| 0 | 0 | 1 | 0 |

|

Bits 13 to 3: Maximum Frame Size (MXFRM10 to MXFRM0). These bits indicate the maximum packet size value. All transmitted frames larger than this value are counted as long frames.

Bit 1: Reserved. Note that this bit must be written to a “1” for proper operation.

130 of 167