DS33Z41 Quad IMUX Ethernet Mapper

Register Name: |

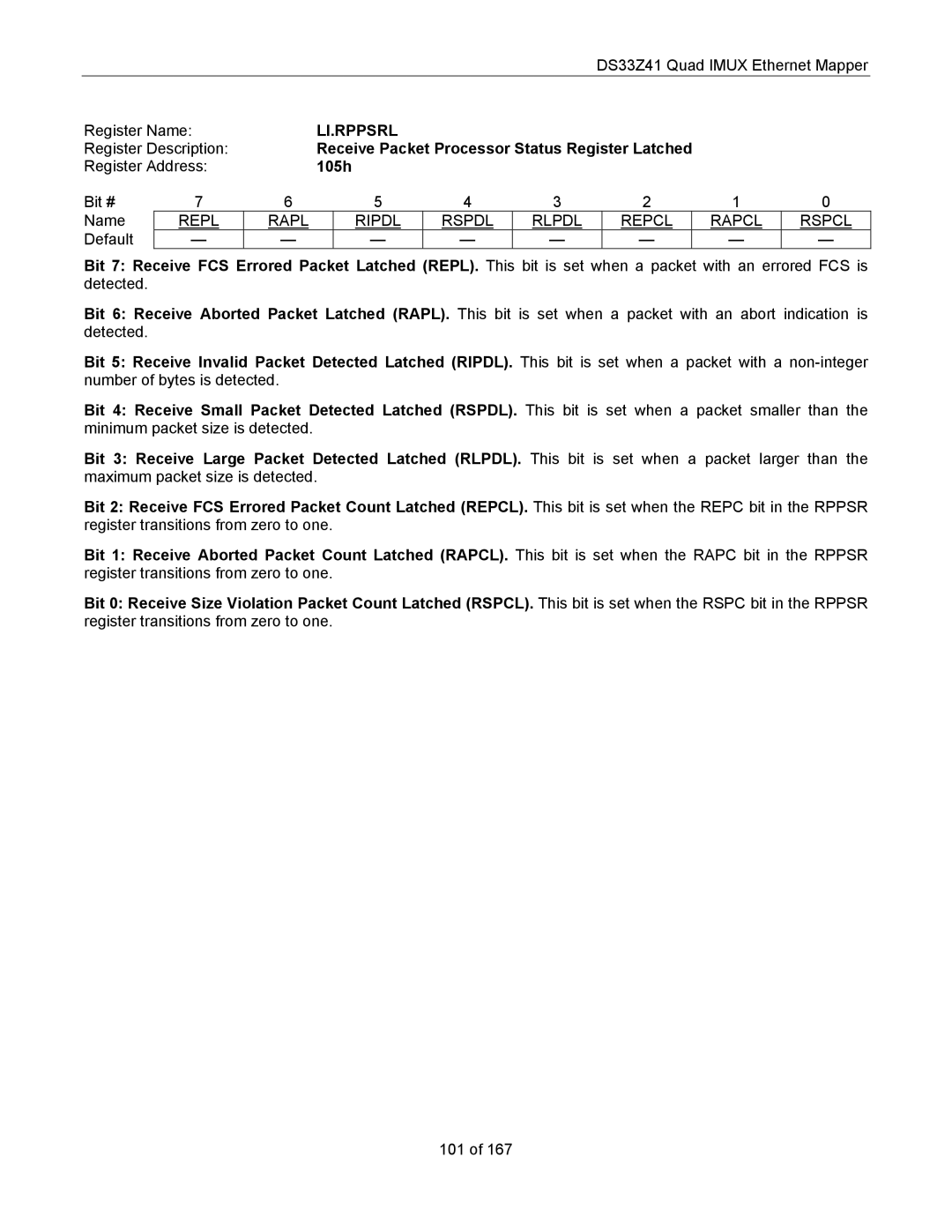

| LI.RPPSRL |

|

|

|

|

|

| ||

Register Description: |

| Receive Packet Processor Status Register Latched |

|

| ||||||

Register Address: |

| 105h |

|

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 |

| 1 | 0 | |

Name | REPL | RAPL |

| RIPDL | RSPDL | RLPDL | REPCL |

| RAPCL | RSPCL |

Default | — | — |

| — | — | — | — |

| — | — |

Bit 7: Receive FCS Errored Packet Latched (REPL). This bit is set when a packet with an errored FCS is detected.

Bit 6: Receive Aborted Packet Latched (RAPL). This bit is set when a packet with an abort indication is detected.

Bit 5: Receive Invalid Packet Detected Latched (RIPDL). This bit is set when a packet with a

Bit 4: Receive Small Packet Detected Latched (RSPDL). This bit is set when a packet smaller than the minimum packet size is detected.

Bit 3: Receive Large Packet Detected Latched (RLPDL). This bit is set when a packet larger than the maximum packet size is detected.

Bit 2: Receive FCS Errored Packet Count Latched (REPCL). This bit is set when the REPC bit in the RPPSR register transitions from zero to one.

Bit 1: Receive Aborted Packet Count Latched (RAPCL). This bit is set when the RAPC bit in the RPPSR register transitions from zero to one.

Bit 0: Receive Size Violation Packet Count Latched (RSPCL). This bit is set when the RSPC bit in the RPPSR register transitions from zero to one.

101 of 167