DS33Z41 Quad IMUX Ethernet Mapper

9.5.4X.86 Registers

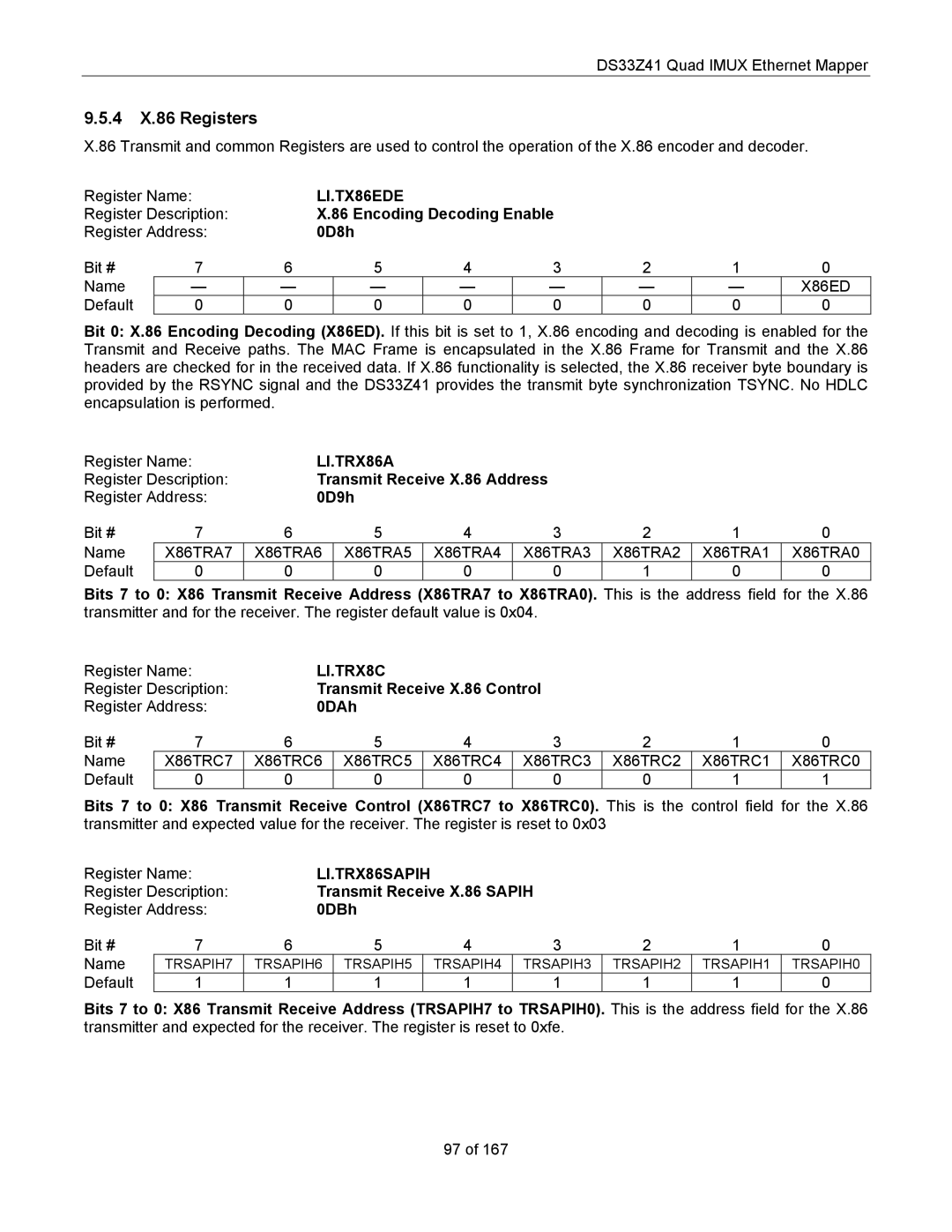

X.86 Transmit and common Registers are used to control the operation of the X.86 encoder and decoder.

Register Name: |

| LI.TX86EDE |

|

|

|

|

| ||

Register Description: |

| X.86 Encoding Decoding Enable |

|

|

| ||||

Register Address: |

| 0D8h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | — | — |

| — | — | — | — | — | X86ED |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

Bit 0: X.86 Encoding Decoding (X86ED). If this bit is set to 1, X.86 encoding and decoding is enabled for the Transmit and Receive paths. The MAC Frame is encapsulated in the X.86 Frame for Transmit and the X.86 headers are checked for in the received data. If X.86 functionality is selected, the X.86 receiver byte boundary is provided by the RSYNC signal and the DS33Z41 provides the transmit byte synchronization TSYNC. No HDLC encapsulation is performed.

Register Name: | LI.TRX86A |

|

|

|

|

| ||

Register Description: | Transmit Receive X.86 Address |

|

|

| ||||

Register Address: | 0D9h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Name | X86TRA7 | X86TRA6 | X86TRA5 | X86TRA4 | X86TRA3 | X86TRA2 | X86TRA1 | X86TRA0 |

Default | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

Bits 7 to 0: X86 Transmit Receive Address (X86TRA7 to X86TRA0). This is the address field for the X.86 transmitter and for the receiver. The register default value is 0x04.

Register Name: | LI.TRX8C |

|

|

|

|

| ||

Register Description: | Transmit Receive X.86 Control |

|

|

| ||||

Register Address: | 0DAh |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Name | X86TRC7 | X86TRC6 | X86TRC5 | X86TRC4 | X86TRC3 | X86TRC2 | X86TRC1 | X86TRC0 |

Default | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

Bits 7 to 0: X86 Transmit Receive Control (X86TRC7 to X86TRC0). This is the control field for the X.86 transmitter and expected value for the receiver. The register is reset to 0x03

Register Name: | LI.TRX86SAPIH |

|

|

|

|

| |||

Register Description: | Transmit Receive X.86 SAPIH |

|

|

| |||||

Register Address: | 0DBh |

|

|

|

|

| |||

Bit # | 7 | 6 | 5 |

| 4 | 3 | 2 | 1 | 0 |

Name | TRSAPIH7 | TRSAPIH6 | TRSAPIH5 |

| TRSAPIH4 | TRSAPIH3 | TRSAPIH2 | TRSAPIH1 | TRSAPIH0 |

Default | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 |

Bits 7 to 0: X86 Transmit Receive Address (TRSAPIH7 to TRSAPIH0). This is the address field for the X.86 transmitter and expected for the receiver. The register is reset to 0xfe.

97 of 167