DS33Z41 Quad IMUX Ethernet Mapper

9.4BERT Registers

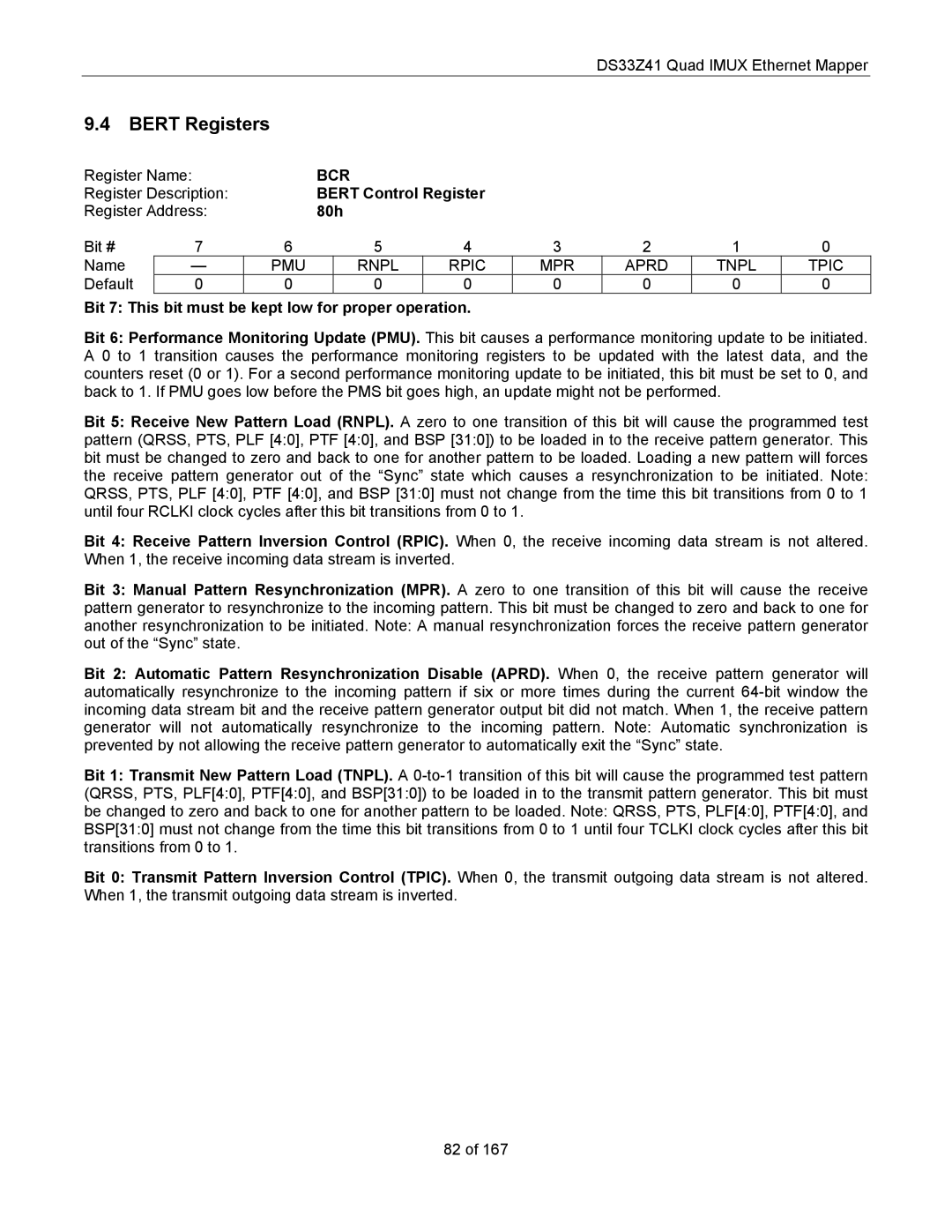

Register Name: |

| BCR |

|

|

|

|

| ||

Register Description: |

| BERT Control Register |

|

|

|

| |||

Register Address: |

| 80h |

|

|

|

|

| ||

Bit # | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

Name | — | PMU |

| RNPL | RPIC | MPR | APRD | TNPL | TPIC |

Default | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 |

Bit 7: This bit must be kept low for proper operation.

Bit 6: Performance Monitoring Update (PMU). This bit causes a performance monitoring update to be initiated. A 0 to 1 transition causes the performance monitoring registers to be updated with the latest data, and the counters reset (0 or 1). For a second performance monitoring update to be initiated, this bit must be set to 0, and back to 1. If PMU goes low before the PMS bit goes high, an update might not be performed.

Bit 5: Receive New Pattern Load (RNPL). A zero to one transition of this bit will cause the programmed test pattern (QRSS, PTS, PLF [4:0], PTF [4:0], and BSP [31:0]) to be loaded in to the receive pattern generator. This bit must be changed to zero and back to one for another pattern to be loaded. Loading a new pattern will forces the receive pattern generator out of the “Sync” state which causes a resynchronization to be initiated. Note: QRSS, PTS, PLF [4:0], PTF [4:0], and BSP [31:0] must not change from the time this bit transitions from 0 to 1 until four RCLKI clock cycles after this bit transitions from 0 to 1.

Bit 4: Receive Pattern Inversion Control (RPIC). When 0, the receive incoming data stream is not altered. When 1, the receive incoming data stream is inverted.

Bit 3: Manual Pattern Resynchronization (MPR). A zero to one transition of this bit will cause the receive pattern generator to resynchronize to the incoming pattern. This bit must be changed to zero and back to one for another resynchronization to be initiated. Note: A manual resynchronization forces the receive pattern generator out of the “Sync” state.

Bit 2: Automatic Pattern Resynchronization Disable (APRD). When 0, the receive pattern generator will automatically resynchronize to the incoming pattern if six or more times during the current

Bit 1: Transmit New Pattern Load (TNPL). A

Bit 0: Transmit Pattern Inversion Control (TPIC). When 0, the transmit outgoing data stream is not altered. When 1, the transmit outgoing data stream is inverted.

82 of 167